Part Number: DAC39RF12EVM

Other Parts Discussed in Thread: TSW14J59EVM

Tool/software:

Hello,

I am currently working with the DAC39RF12EVM board connected to the TSW14J59EVM board, and I followed the procedure in the User Guide to download and run the program. However, I have encountered several issues and would like to ask for your advice.

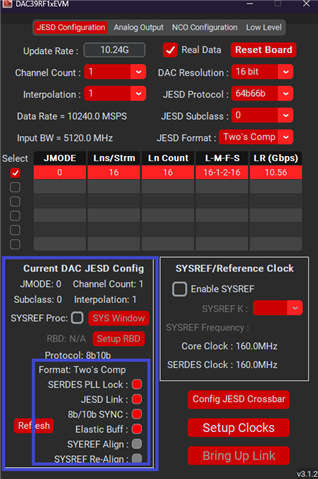

At the initial execution stage, the JESD Config status indicator does not turn green as shown in the User Guide figures.

Ignoring this, I proceeded with the User Guide steps and set JMODE0, but the expected 4 GHz single tone output was not observed on the spectrum analyzer. Even after completing all of the settings, the JESD Config status indicator still does not turn green.

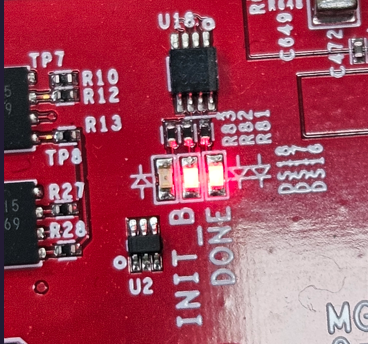

In addition, the LED status on the TSW14J59 board changed as shown in the attached photo, and I am not sure if this indicates normal operation.

Finally, after Figure 2-7 in the User Guide, is there any additional button or step that I need to execute?

For reference, I have also attached the j59 server log. Please let me know if I am missing any procedure or if my configuration is incorrect. I would also appreciate clarification on whether any separate jumper settings on the TSW14J59EVM board are required.

Thank you.

***Surveying the landscape for connected FPGAs...

***One FPGA detected. The Cable ID is 210251B73228

***Checking connected boards for J59 FPGA compatibility

***Found a J59 compatible Kintex UltraScale+ FPGA on Board 0

***Initializing J59

*** Starting server on port 50000

***Server is listening for connections...

***Connection from test

*** Received message from test: j59.fpga_init()

***Neither bitfile nor protocol specified! Assuming FPGA is already programmed

*** Received message from test: j59.fpga_init(jesd_protocol='64b66b')

***Programming FPGA

***J59 FPGA initialized. Checking supported protocol

***The FPGA is loaded with a 64b66b JESD IP

*** Received message from test: j59.jesd_set_link_rate(lane_rate=10560000000.0, gbtrefclk_ratio=66.0)

***Setting the PLL reference buffer to REFCLK0

***Expecting the PLL reference frequency to be 160.0 MHz

***The PLL selected is QPLL0

***All PLLs locked. PHY is ready

*** Received message from test: j59.dac_set_jesd_params('lmfs_params', Links=1, Lanes=16, Channels=1, Frame_Octets=2, Samples_Per_Frame=16, Frames_Per_Multiframe=32, Channel_Resolution=16, JESD_Sample_Resolution=16, HD_Mode=0, Format_Twos_Complement=True, deinterleaving_factor=None)

***Setting LMFS parameters for the Tx IP

***Lane mapping and inversions will be set to defaults

{'Links': 1,

'Lanes': 16,

'Channels': 1,

'Frame_Octets': 2,

'Samples_Per_Frame': 16,

'Channel_Resolution': 16,

'JESD_Sample_Resolution': 16,

'Format_Twos_Complement': True,

'HD_Mode': 0,

'Frames_Per_Multiframe': 32,

'MBlocks_Per_EMBlock': 1,

'Scrambling': 1,

'lane_map': [0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15],

'inverted_lanes': [0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0],

'active_lanes': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1],

'deinterleaving_factor': None}

*** Received message from test: j59.dac_link_bringup()

*** Received message from test: j59.dac_load_buffer(csv_file='C:/Users/user/Documents/Texas Instruments/DAC39RF12EVM_SW_Package/v3.1.2/J59 Commander/dac_tones/temp.csv', start_address ='RAM1')

***Buffer loaded. Total size of buffer is 245760

*** Received message from test: j59.dac_setup_playback(playback_buffer_start_address='RAM1', buffer_size=245760)

***Setting up DAC playback buffer and parameters

{'lane_playback_order': [0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15],

'playback_buffer_start_address': 'RAM1',

'buffer_size': 245760,

'cyclic_mode': True,

'trig_source': 'sw',

'trig_delay': 0,

'start_on_multiframe': False,

'wait_multiframe_boundary': False}

*** Received message from test: j59.dac_playback_start()

*** Received message from test: quit

***Sent 'quit accepted' to test. Closing connection.

***Connection from test closed.