Tool/software:

Hi,

In the "Related Questions" section, I will ask additional questions based on my previous interactions with the manufacturer's engineers.

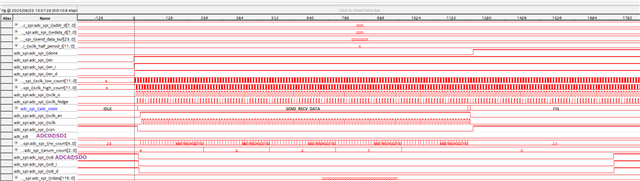

We are currently supporting a customer evaluating the ADS7066IYBHT in a 5-device daisy chain configuration, and would like to confirm the following technical details regarding the SPI behavior.

1. Daisy Chain Receive Order

In the following configuration:

We understand that the input data (SDI) propagates through the chain such that each ADC receives its 24-bit command in reverse order as follows:

-

Clocks 1–24: ADC4 receives

-

Clocks 25–48: ADC3

-

Clocks 49–72: ADC2

-

Clocks 73–96: ADC1

-

Clocks 97–120: ADC0

Could you please confirm whether this interpretation matches the internal shift register behavior described in the datasheet section 7.3.10.2 Daisy-Chain Mode?

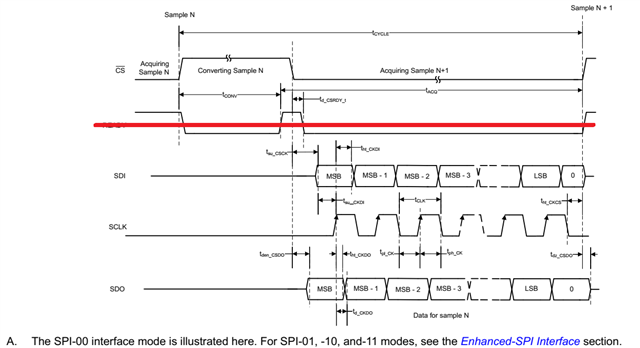

2. SPI-00 Protocol Timing Behavior

Regarding the SPI-00 protocol (default), our understanding is:

-

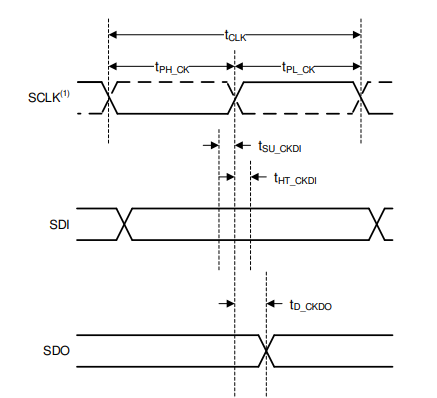

SDI is latched on SCLK rising edge

-

SDO updates on SCLK falling edge

Additionally, we would appreciate your clarification on:

-

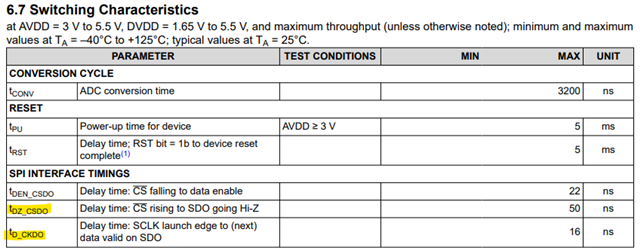

Page 9 of the datasheet (Figure 6-3) appears to imply:

-

SDO becomes valid after CS falling edge +

tDEN_CSDO -

SDO toggles after SCLK rising edge +

tD_CKDO

-

-

However, we could not find explicit timing definitions for tDEN_CSDO or tD_CKDO in the electrical characteristics table.

Do you have more detailed SPI timing charts (such as SCLK / SDI / SDO waveform diagrams), especially for Daisy Chain mode in SPI-00, that you could share?

Thanks,

Conor