Tool/software:

Dear TI team,

I have performed some measurements of the ADC latency (SMPL_CLK to data on the data lanes) in two different configurations. I have a question about a delay I didn't understand in the second configuration I tested.

I connected a square signal generator to the ADC input and checked the data stream at the ADC output to see the step in the data.

Case 1: 2-lane output and decimation disabled

The ADCs are configured as follows:

Register 0xFB -> 0x0000

Register 0x0D -> 0x2382

In this case, I measured a latency close to 112 ns with jitter ranging from 0 to 50 ns.

The jitter of 50 ns makes sense, as the square signal was not synchronized with the sampling clock.

The 112 ns corresponds to the delay specified in the datasheet (page 11, td_SMPL_DATA), so the measurement seems correct.

Case 2: 1-lane output and decimation set to 2 samples averaged

The ADCs are configured as follows:

Register 0xFB -> 0x0002

Register 0x0D -> 0x23C2

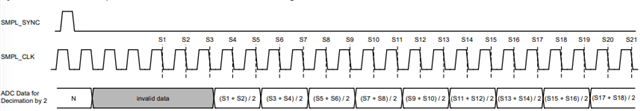

In this case, I measured a latency of around 225 ns with a jitter of 0 to 100 ns.

A jitter of 100 ns makes sense, as we are averaging two samples with a sampling period of 50 ns.

However, I don't understand why the latency increased by around 113 ns.

Do you know what the reason for this higher latency is?

Does enabling decimation increase the latency?

Looking forward to your reply,