Other Parts Discussed in Thread: ADC09DJ1300

Tool/software:

Hello, experts,

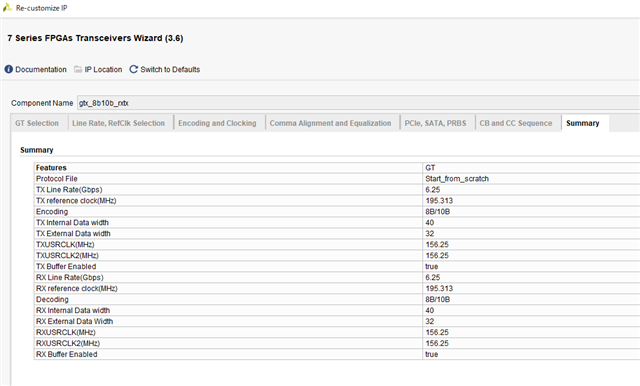

I'm having trouble resolving a pulse width errors in Vivado timing analysis.

(Error screen)

Is the operation of the ADC09DJ1300 and TI-JESD204C-IP guaranteed with this configuration?

Is it even possible to use them with this setup?

If there are any settings I might have overlooked, please advise.