Part Number: ADS124S08

Tool/software:

As I mentioned earlier, I implemented the software to read analog values using the ASD124S08. While testing the communication, I came across some questions that I’d like to ask.

First, I used the Continuous Conversion Mode for data conversion. At initialization, I set the registers as shown below, then periodically updated the INPMUX and IDACMUX values, switching channels and reading different analog inputs using the RDATA command.

ID: 0x00 (ADS124S08)

STATUS: 0x80

INPMUX: Channel1 (AIN1, AIN2), Channel2 (AIN5, AIN6), Channel3 (AIN9, AIN10)

PGA: 0xEA

DATARATE: 0x14

REF: 0x01

IDACMAG: 0x07

IDACMUX: Channel1 (AIN3, AIN0), Channel2 (AIN7, AIN4), Channel3 (AIN11, AIN8)

VBIAS: 0x00

SYS: 0x10

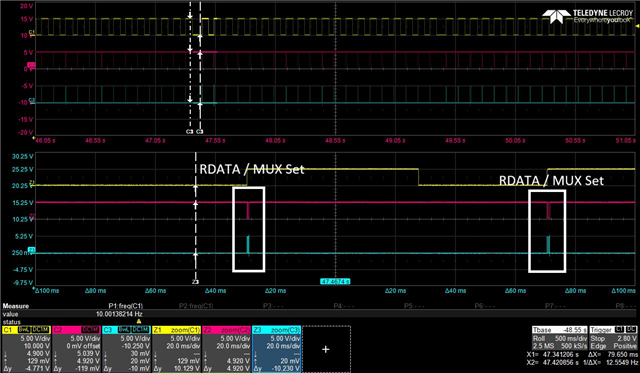

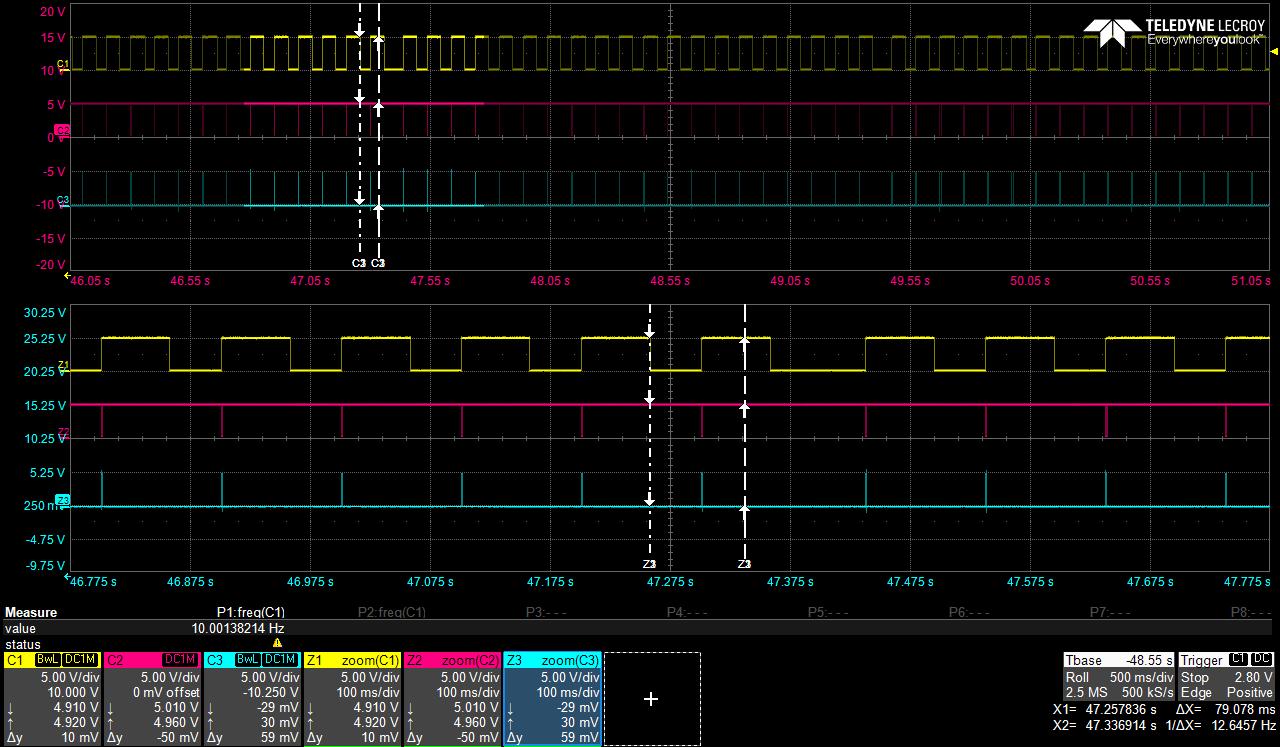

In this way, I confirmed the waveforms shown in the attached image: yellow = DRDY, red = CS, blue = SCLK.

Here are my questions:

-

I set SPS = 20, so I expected the DRDY (HIGH period) to correspond to a conversion time of about 50 ms. In fact, I measured it at 53–57 ms. Is this 3–7 ms deviation caused by conversion delay?

Currently, the PGA setting is configured as 1 × tMOD. Could this setting be affecting the timing? -

I also want to clarify the exact condition for when DRDY goes LOW. While the LOW duration is usually consistent, I sometimes observe it being maintained longer. Since I am using continuous conversion, I thought the DRDY timing would be determined strictly by the SPS setting, but it doesn’t seem consistent. I tested changing the PGA delay setting, but it didn’t affect this behavior. Could you please explain why this happens?

-

As I mentioned, I periodically update the INPMUX and IDACMUX registers using the WREG command, then read the data using RDATA. However, unless I add a delay of about 100 ms after changing the MUX settings, no valid data is read. If I reduce the delay to 50 ms, I still get invalid results. I understand that some delay should be needed after switching the MUX, but requiring such a long delay seems unusual, so I suspect I may be doing something incorrectly.

-

In the image, the longer blue waveform on the right shows the part where I set INPMUX and IDACMUX one by one using WREG, while the left side shows the RDATA portion of the previous cycle.

In fact, after setting INPMUX and IDACMUX with WREG, I then wait until the next DRDY goes LOW and then HIGH again, and at that point I read the data using RDATA. Could you please advise if you know what state this behavior corresponds to, or what I might be missing?