Tool/software:

Hi,

We use the DAC121C081 in our project, and now, please advise Is there anything important about the High Speed (3.4-MHz) Modes circuit on this chip?

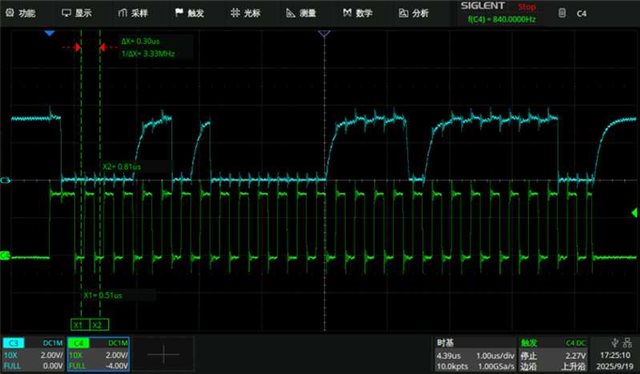

We are currently facing a problem where adjusting the I2C input under special circumstances may result in the chip having no output after refreshing tens of thousands of times.

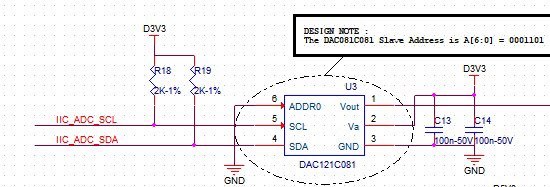

The below is our schematic diagram?