Other Parts Discussed in Thread: ADC31JB68,

Tool/software:

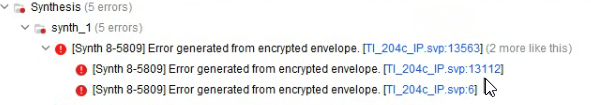

I'm trying to get the TI-JESD204-IP working on an Artix-7 (xc7a100tfgg484-2) to communicate with the TI ADC ADC31JB68.

I'm getting a little confused on how to get the initial project set up. Reading the TI204C-IP-Users-Guide.pdf it recommends first loading the reference design zc706_8b10b for the Artix-7 and then following the directions below. I've add in my comments (in RED) for where I'm getting confused

- Open the transceiver wizard and note down all the settings on all the pages of the wizard. This will be important in step <4> below, because the same settings will need to be created for the transceiver on the new FPGA : The zc706 design is a GTX transiever running at 6.25 Gbps and the Artix-7 (that I'm using) is a GTP 3.125 Gbps. It does not seem like copying those settings would make sense but there does not seem to be an actual Artix-7 reference design to copy the files from. How do I handle this part? I tried to look a the mgt_8b10b_wrap (gtx_8b19b_rxtx.sv) to see if I could reverse engineer what I needed to provide it but its pretty complicated with many wires. Also it supports TX and RX and I only need RX.

- Save the original tested project as a new project with the new FPGA / DevKit set as the target device/board. Choose the option to copy all the source files, IPs and constraints.

Is this really the only way to add in the TI_JESD_IP? I already have an existing design and would really just prefer to import the TI_JESD_IP into it and instantiate it and mostly that seems pretty simple but the part that I'm not sure how to do is the mgt_8b10b_wrap, how do I get that one for just an Artix-7 with RX support only?

Thanks in advance for any help!