Tool/software:

Hi Support Team,

I would like to achieve exactly 10 kSPS sampling rate synchronized to an external 10 kHz signal's rising edge.

Board Configuration:

- FPGA connected to ADS131M02

- 2 ADC input channels

- Single-ended input: AINnP only (AINnN connected to GND)

My Strategy:

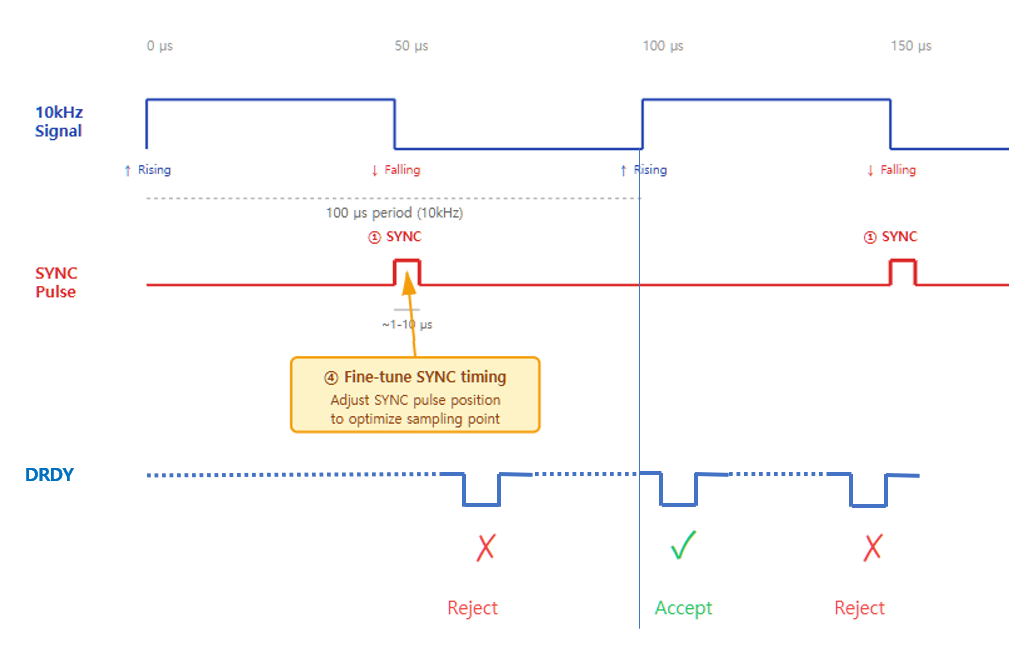

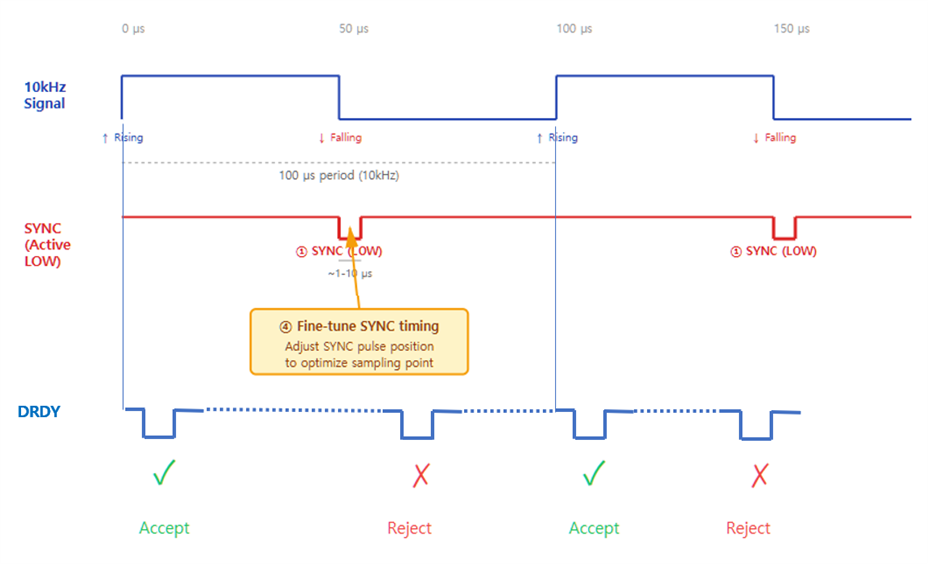

- Configure ADC for 64 kSPS in continuous-conversion mode

- Send SYNC pulse synchronized to the external 10 kHz signal's falling edge

- Read all ADC samples at every DRDY falling edge

- Accept only the ADC data sampled immediately after the 10 kHz rising edge

- Adjust when the SYNC pulse is generated to fine-tune where the sampling occurs within each 10 kHz period

Questions:

- Is this approach reasonable and feasible?

- Are there any recommended best practices or potential issues I should be aware of?

- Would phase calibration be helpful in this application?

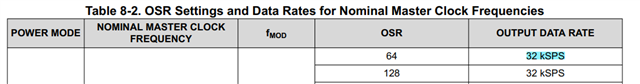

BTW there seems to be a typo at table 8-2 of the datasheet( SBAS853A – JANUARY 2020 – REVISED APRIL 2021 )

I think OSR 64 corresponds to 64kSPS

Thank you for your assistance.

Best regards,

Jason Lee