Other Parts Discussed in Thread: ADC168M102R-SEP

Tool/software:

I am working with the evaluation module for the ADC168M102R-SEP. I intend to use it with full clock mode and pseudo-differential mode. I am unable to get analysis sampling of all 8 channels when when using the ADC168M102REVM-PDK-GUI. The board is set up with CMA/CMB tied to internal VREF. All analog inputs are tied to common. Please advise how to configure and operate to demonstrate readout of 8 input analog channels in full clock mode.

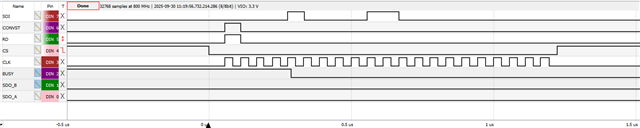

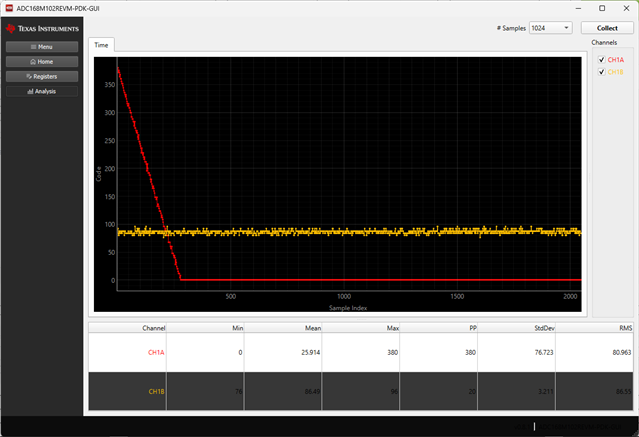

When setting the config register to 0x10C0 (full clock mode and pseudo-differential mode) with Mode 3 (confirmed that M0 = 1, M1 = 0), then when collecting samples it only reports CH1A and CH1B. Below are images for setting the config register, and then collecting 1024 samples

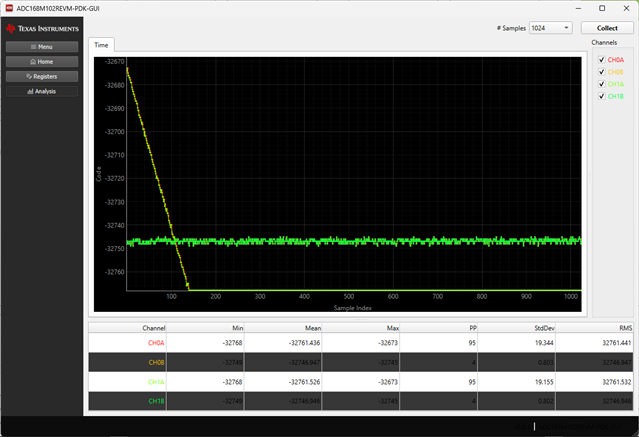

If I sample with config register 0x10C0 and in Mode 1 (confirmed that M0 = 0, M1 = 0) then it reports CH0A, CH0B, CH1A, CH1B: