Other Parts Discussed in Thread: ADS54J60EVM

Tool/software:

Hi Experts

I have difficulty in implementing JESD204 IP receiver in FPGA zcu102 board .

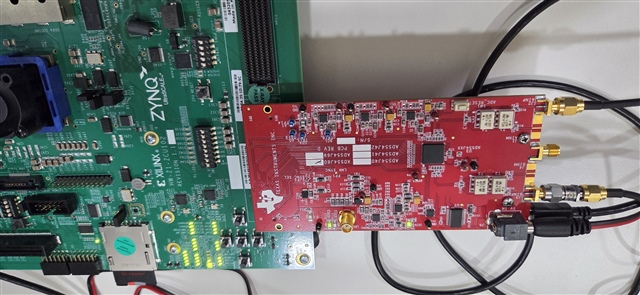

Firstly I have checked the ADC ADS54J60EVM using TSW14J50. (SERDES= 4.9152Gb/s, Device frequeny =983.04 MHz, LMFS=8224, Function generator frequency 100 MHz 10dBm power for CHA and 100 MHz 4 dBm for CHB) It successfully worked as shown in below

Next I have simulated TI JESD204 IP setting IP_TYPE "RXTX". In the simulation of TI_204c_IP_ref, my gth_8b10b_xcvr is shown in the two figures below

The refclk 245.76 MHz is used to generate an additional 245.76 MHz mgt_gpio_out clk using BUFG_GT. This mgt_gpio_out is used clk_in input for sys_pll which generates two identical frequency 61.44 MHz sys_clock and mgt_freerun_clock. By passing vio_inst in TI_204c_IP_ref. The simulation successfully works. Finally I made bit file for the receiver setting IP_TYPE "RX". The setting is shown in photo as below.

The measured results are shown in below and unfortunately rx_lane_data_valid stays to 0 and all rx_data 0 as a result.

I don't know why the ADC receiver does not work. At first I used FPGA clock such as si570 but the sys_clock and mgt_freerun clock frequencies are not exact. So I made change using mgt_gpio_out whose frequency is exactly equal to refclk. I want help to make the ADC receiver work. Thank you in advance.

Regards

K.W. Yeom