Other Parts Discussed in Thread: TSWDC155EVM, , THS4552, ADS9813, ADS7853, ADS7253, ADS8355

Tool/software:

Hi, I got development board TSWDC155EVM and ADS9327EVM

when I lunch the your software (ADS9327EVD-GUI)

I got this error

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Kouhmareh,

Welcome to TI's E2E forum!

Could you please let me know the version of the software that was installed? Is it the same version as the one available https://www.ti.com/tool/download/ADS9327EVM-GUI?

Would you also be able to show the current HW configuration of both the TSWDC155EVM and the ADS9327EVM? A picture would help, but at least a description of the jumpers/shunts populated on both boards

Best regards,

Yolanda

Hello Kouhmareh,

Could you also scroll down to the bottom of the error window to see the full error message? or if you could copy and paste the full text that would also be helpful.

Thank you,

Yolanda

Hello Kouhmareh,

An updated version of the GUI has been released to fix the issue share, could you please install the latest version of the GUI and see if the issue is still there?

Thank you,

Yolanda

I have anoter question I am using ADS9327, in One line configuration , when try to read new data conversion , all bit are zero

here is my setting

UART_PutString("****** ADC ADS9327 Reg_Initilzation......******\r\n");

SPI_CS_MUX_Write(0x00); // ADC_ChSel 1,2

SPIM_AFE_Write(0x01); //add

SPIM_AFE_Write(0x00); //reset

SPIM_AFE_Write(0x02); //reset

CyDelay(1); // requier by datasheey

SPIM_AFE_Write(0x01); // add

SPIM_AFE_Write(0x00); // remove reset

SPIM_AFE_Write(0x00); // remove reset

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xB3); // UNLOCK Frame1

SPIM_AFE_Write(0x8F); // UNLOCK Frame1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xAB); // UNLOCK Frame2

SPIM_AFE_Write(0xCD); // UNLOCK Frame2

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x02); // add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x02); // sel reg bank 1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x0C); // add

SPIM_AFE_Write(0x12); // internal ref is active

SPIM_AFE_Write(0x00); // internal ref is active

CyDelay(25); // requier by datasheey

SPIM_AFE_Write(0x0C); // add

SPIM_AFE_Write(0x02); // internal ref is active

SPIM_AFE_Write(0x00); // internal ref is active

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x03); // add

SPIM_AFE_Write(0x00); // unlock reg bank2

SPIM_AFE_Write(0x0B); // sel reg bank 2

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x02); // add

SPIM_AFE_Write(0x00); // unlock reg bank2

SPIM_AFE_Write(0x08); //

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x22); // add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x80); // init_2 = 1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x02); // add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x02); // init_2 = 1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0x12); // LOCK Frame1

SPIM_AFE_Write(0x34); // LOCK Frame1

CyDelayUs(microsecDelay);

//***************** Write Registers *******************//

if(WriteReg == 0x01){

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xB3); // UNLOCK Frame1

SPIM_AFE_Write(0x8F); // UNLOCK Frame1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xAB); // UNLOCK Frame2

SPIM_AFE_Write(0xCD); // UNLOCK Frame2

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x02); // add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x02); // sel reg bank 1

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x09); //add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x60); // data on D3 only

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x0D); //add

SPIM_AFE_Write(0x01); // = Straight-binary format; CRC module is inactive

SPIM_AFE_Write(0x00); // Simple averaging is inactive;

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); //add

SPIM_AFE_Write(0x12); //

SPIM_AFE_Write(0x34); // data on D3 only

CyDelayUs(microsecDelay);

WriteReg = 0x00;

}

//***************** Read Registers *******************//

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xB3); // UNLOCK Frame1

SPIM_AFE_Write(0x8F); // UNLOCK Frame1

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0xAB); // UNLOCK Frame2

SPIM_AFE_Write(0xCD); // UNLOCK Frame2

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x02); // add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x02); // sel reg bank 1

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

CyDelayUs(microsecDelay);

SPIM_AFE_Write(0x01); //add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x01); // data on D3 only

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

CyDelayUs(microsecDelay);

//-------------------------------------------------------

Cy_GPIO_Write(P9_2_PORT, P9_2_NUM, 0x01); // stat thaking ADC sample

CyDelayUs(2);

Cy_GPIO_Write(P9_2_PORT, P9_2_NUM, 0x00); // stat thaking ADC sample

CyDelayUs(1);

SPIM_AFE_Write(0x01); //add

SPIM_AFE_Write(0x00); //

SPIM_AFE_Write(0x00); // data on D3 only

SPIM_AFE_Write(0x00);

SPIM_AFE_Write(0x00);

SPIM_AFE_Write(0x00);

// CyDelayUs(microsecDelay);

ADC_data1 = SPIM_AFE_Read(); //Read CH 1

ADC_data2 = SPIM_AFE_Read();

ADC_data3 = SPIM_AFE_Read();

// CyDelayUs(microsecDelay);

ADC_data4 = SPIM_AFE_Read(); //Read CH 2

ADC_data2 = SPIM_AFE_Read();

ADC_data3 = SPIM_AFE_Read();

CyDelayUs(microsecDelay);

//-----------------------------------------------

SPIM_AFE_Write(0xFE); // add

SPIM_AFE_Write(0x12); // UNLOCK Frame1

SPIM_AFE_Write(0x34); // UNLOCK Frame1

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

SPIM_AFE_Write(0x00); // to make it 48 clk fram

CyDelayUs(microsecDelay);

Hello Kouhmareh,

I have a few comments:

Best regards,

Yolanda

Yolanda , could you please look at my setting , do I mess any thig

| Table 7-7. ADS932x Initialization Sequence | ||||

| STEP NUMBER | REGISTER | |||

| BANK | ADDRESS | VALUE[15:0] | ||

| 1 | 0 | 0x01 | 0x0002 | |

| 2 | Wait 1ms | |||

| 3 | 0 | 0x01 | 0x0000 | |

| 4 | 0 | 0xFE | 0xB38F | |

| 5 | 0 | 0xFE | 0xABCD | |

| 6 | 0 | 0x02 | 0x0002 | |

| 7 | 1 | 0x0C | 0x1200 | |

| 8 | Wait 25mSec | |||

| 9 | 1 | 0x0C | 0x0200 | |

| 10 | 0 | 0x03 | 0x000B | |

| 11 | 0 | 0x02 | 0x0008 | |

| 12 | 2 | 0x22 | 0x0080 | |

| 13 | 0 | 0x02 | 0x0002 | |

| 14 | 0 | 0xFE | 0x1234 | |

| Table 7-11. Register Write Sequence | ||||

| STEP NUMBER | REGISTER | |||

| BANK | ADDRESS | VALUE[15:0] | Note | |

| 1 | 0 | 0xFE | 0xB38F | |

| 2 | 0 | 0xFE | 0xABCD | |

| 3 | 0 | 0x01 | 0x0002 | Reset |

| 4 | Wait 1ms | |||

| 5 | 0 | 0x01 | 0x0000 | Remove reset |

| 6 | 0x02 | 0x02 | ||

| 7 | 0x0D | x0100 | Avrg. Inactive; binary out; No CRC | |

| 8 | 0x09 | 0x0460 | Data on D3 ;Low-latecy mode | |

| 0xFE | 0x1234 | Proving 48 clk pulse here | ||

| Table 7-11. Register Read Sequence | ||||

| STEP NUMBER | REGISTER | |||

| BANK | ADDRESS | VALUE[15:0] | Note | |

| 1 | 0xFE | 0xB38F | 48clk puls | |

| 2 | 0xFE | 0xABCD | 48clk puls | |

| 3 | 0x01 | 0x0001 | 48clk puls | |

| 4 | 0x00 | 0x000000 | reading Conversion data here | |

| 5 | 0xFE | 0x1234 | Proving 48 clk pulse here | |

by the way this sequence you mention is contradic with table 7-7 (should be Reset first then unluck Reg)

Hello Kouhmareh,

You are correct, the Table 7-7 does not include the initial register unlock that is needed, this will be changed in the next datasheet update soon.

You only need to do the reset during the initialization process. If you reset the device every time you write to the registers this will undo all the configurations done during initialization.

So the steps should be:

___________________________________________________________________________________________________________________________

The last table you shared is not needed (copied below). What that is doing is enabling a register map read.

The ADC conversion data will come out on D3 after setting DATA_SEL = 0.

You only need to do this when you want to read back a value from a register in the register map.

Table 7-11. Register Read Sequence STEP NUMBER REGISTER BANK ADDRESS VALUE[15:0] Note 1 0xFE 0xB38F 48clk puls 2 0xFE 0xABCD 48clk puls 3 0x01 0x0001 48clk puls 4 0x00 0x000000 reading Conversion data here 5 0xFE 0x1234 Proving 48 clk pulse here

Best regards,

Yolanda

Hello Kouhmareh,

What are the inputs on channel A & B?

Because the data format is {ADCA[15:0],0x00,ADCB[15:0],0x00} I suspect your logic analyzer might be reading the data wrong or there is a timing issue that needs to be adjusted with the communication.

Would 0x603E make more sense for ADC A? it does appear that ADC B has a full scale read, is the input on that channel more than 4.096V (or more than 8.192V differential?) Could you also confirm the common more value of both channels?

Could you share a more zoomed in screen shot of the data analysis or would you have a way to collect this with an oscilloscope?

Best regards,

Yolanda

Hi Yolanda

the input to ADCA is DC input , I start at 0V increase to 2.0V step by step, but ADCA output most of this is constant.

I will share the all setting , I do before I reading ADC conversion data.(tomorrow)

one question, When you reset the ADS9327 what value should I expect at D3? (should be all zero or all one)

by the way D3 still send constant data out?(when reset happen)

I can not read any register ether,(I try to replace the ADS9327)

Do you know any read Register I can do to verify this IC is working)

thanks

Hello Kouhmareh,

DC input is ok, is it still going through the THS on the EVM? Please make sure that the input common mode meets the requirements

At start-up the device is configured with 4-lane mode, so all D[3:0] will be output ADC convert data. The initial data should be ignored right after power up though.

Most registers are set to 0h by default so to confirm functionality I would recommend configuring a register and reading back on D3.

If you currently cannot read any register back then there is a timing issue in the data communication. Could you please share more information on how the timing is configured? What is the SCLK frequency? What about the SAMPL_CLK frequency?

Best regards,

Yolanda

Hi Yolanda, Attached zip file are spi timing , I also .CSV file is all timind detail is there

I also verify timg and data usimg oscillosco

Hello Kouhmareh,

Thank you for sharing the SPI timing, the SPI_2_ADS9327 looks good. I haven't looked through the full excel file yet, but could you please share the common mode measurements as well as what the inputs look at the AIN pins?

Best regards,

Yolanda

Hello Kouhmareh,

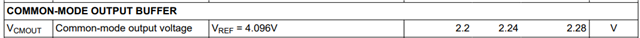

The ADS9327 is a differential input SAR ADC, and it requires that the AINP-AINM have a common mode input of VCMOUT ± 0.4V. VCMOUT should be 2.24V ± 0.04V.

If using the ADS9327EVM you can short one of the AINM signal paths before the THS4552 via J14, J16, or J8 or J10 and input your signal on AINP via J9 or J7. This would work because the common mode will be taken care of by the THS4552.

If the THS4552 is skipped and inputs are directly input to the AINP/AINM of the ADS9327 then extra care is needed to ensure that the input common mode requirements are met as well as that the source used can the drive the inputs of the ADS9327.

From the picture you shared it appears that the THS4552 is being skipped and input common mode is not being accounted for.

Could you please try this test with those inputs before the THS4552?

Additionally I will like to add that this device does have a planned single-ended version to be released soon. The current version though is not capable of single ended functionality.

Best regards,

Yolanda

One basic question, If I proved at the ADS9327 pin AINP = 1.6v and at pin AINM = .6v ,

is this Worked?

Hello Kouhmareh,

AINP = 1.6V and at pin AINM = 0.6V would have an input common mode of 1.1V, this would be outside the recommended parameters of the ADS9327

Input common mode = (AINP + AINM)/2 --> this should be 2.24V ± 0.04V

If you add the common mode to your 1V delta, then AINP = 2.74V and AINM = 1.74V, then the common mode would be 2.24V which would be within the range.

Best regards,

Yolanda

So, there is no way this part worked, if delta voltage between AINP - AINM = .6v, right

if this is a case , when the single end will be release

If you put the AINP - AINM = .6v input on the THS4552 yes, it should work. The signal needs to be driven anyway.

Would it be possible to use it with the THS4552 driving the DC signals you want to test?

The single ended device will be released next year.

Best regards,

Yolanda

Would it be possible to use it with the THS4552 driving the DC signals you want to test? no, i already doing my layout now

I try to ues development board base on my design.

Do you have any replcment part for ADS9327?

I try to use ADC for conversion a signal, change from 1.6v to .9v but it need to be fast enough

to be able to record 5msec drop voltage, here is signal

Pin to pin replacements? No

Other replacements that could measure the 5ms voltage drop, probably. What would be the the sample rate or sample count you would need for the attached signal?

Could anything else be added between your current board and the signal to add a common mode offset?

Best regards,

Yolanda

my design has 32 channel, i am using 16 of these ADC, much easer to replace ic then Common mode offset.

Not looking for pin to pin replacement.

looking for ADC Ic that fast enough for 5 msec multiple sampling has two ch, and SPI interface, 12 or 16 bits

That still leaves a lot of possibilities, could you help me narrow it down a bit?

It seems like you would need a 2-ch Single-Ended ADC with SPI? with at least 12bits ? or would 16+bits be preferred?

When you mention "5msec" multiple sampling, do you mean a single sample every 5 milli-seconds or do you mean 5 million samples per second (5MSPS)?

Also, "multiple sampling" meaning simultaneous sampling? do all 32 channels need to be sampled at the same time or just 2 at a time?

If the measurement frequency is slow, there isn't much concern, but if there is a need to make measurements at around 5MSPS, an ADC Driver plus a kick-back charge RC would be required, or very heavily recommended. For fully differential ADCs a common mode consideration would also be required.

Or looking for an ADC that has integrated driver stage would be best.

We do have some options:

If useful we do have some videos about ADCs that could be helpful: Precision Lab Series: ADC

Best regards,

Yolanda

I try to use this part in battey dischare design, Battery voltage change from 1.6v to 0 volt under discharge load

as you can see from the Discharge waveform

I need 2 ch per ADC, fast enoght to take multiple sample when discharge happen

(by the ADS8355/ADS7853/ADS7253) are good but my sysetem run on 3.3v not 4.0v

If speed isnt an issue then what about the ADS7067, this device has 8 channels, 800ksps, and can work with 3.3V

It is a muxed ADC and not simultaneous sampling, but if 2 devices are synchronized then you can get two simultaneous measurements between them?

-Yolanda