Other Parts Discussed in Thread: AM6442,

Tool/software:

Hello,

We are using the DAC60508ZC device which is connected to MPU AM6442 SPI bus. With respect to SPI lines when we start the communication on SPI bus we could see CS going LOW and also the SCK and MOSI getting toggled accordingly. Since this chip doesn't support SDO functionality we can not confirm if the write is success or not and we can also not read the device ID.

we have made sure that we are writing the CLR-MSK bit for Channel 0 to 3 and Channel 4 to 7 in the GAIN register and also made sure that the internal reference voltage of 2.5V is been generated in the REF pin of the chip.

below is the sequence of register we are writing

1. write CONFIG register with value 0x0

2. write GAIN register with 0xFF

3. write the data to DAC channels

4. setting 4th pin of trigger register to 1

with all these reg setting also we are not able to see any Vout getting generated and it always seems to be 0V. also attached the code snippet for your reference.

Can you confirm if the sequence of the writing the register is correct or any changes is needed in the sequence.

It would be helpful if you provide us with any sample baremetal or c code for this chip.

Below is the code snippet of our application:

#include <stdio.h>

#include <stdint.h>

#include <fcntl.h>

#include <unistd.h>

#include <sys/ioctl.h>

#include <linux/spi/spidev.h>

#define SPI_DEV "/dev/spidev2.0"

#define SPI_MODE SPI_MODE_0

#define SPI_SPEED 1000000 // 1 MHz

#define SPI_BITS 8

// DAC60508 Register Addresses

#define REG_NOP 0x00

#define REG_DEVICE_CONFIG 0x01

#define REG_SHDN 0x02

#define REG_CONFIG 0x03

#define REG_GAIN 0x04

#define REG_TRIGGER 0x05

#define REG_STATUS 0x07

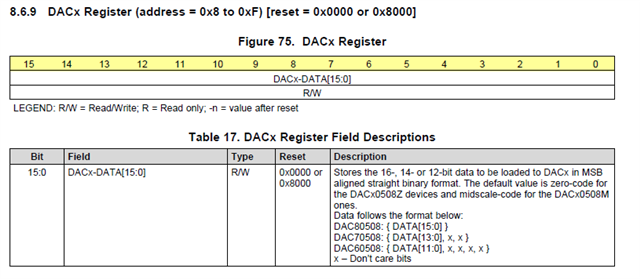

#define REG_DAC_BASE 0x08 // DAC0 = 0x08, DAC7 = 0x0F

// Helper function: write 3 bytes over SPI

static int spi_write_reg(int fd, uint8_t addr, uint16_t value)

{

uint8_t tx[3];

tx[0] = addr;

tx[1] = (value >> 8) & 0xFF;

tx[2] = value & 0xFF;

return write(fd, tx, 3);

}

int main(void)

{

int fd = open(SPI_DEV, O_RDWR);

if (fd < 0) {

perror("open SPI_DEV");

return 1;

}

uint8_t mode = SPI_MODE;

uint32_t speed = SPI_SPEED;

uint8_t bits = SPI_BITS;

ioctl(fd, SPI_IOC_WR_MODE, &mode);

ioctl(fd, SPI_IOC_WR_BITS_PER_WORD, &bits);

ioctl(fd, SPI_IOC_WR_MAX_SPEED_HZ, &speed);

printf("Initializing DAC60508...\n");

// 1. Enable internal reference

// Bit 15 = REF_PWDWN (0 = enable)

spi_write_reg(fd, REG_CONFIG, 0x0000);

usleep(10000); // 10 ms delay for reference to stabilize

// 2. Set gain = ×2 for all channels

// Bits [15:8] = gain for DAC7–DAC0; 0=×1, 1=×2

// Example: 0xFFFF → ×2 gain for all 8 channels

spi_write_reg(fd, REG_GAIN, 0x0FFF);

// 3. Write midscale (0x8000) to all 8 DAC channels (0x08–0x0F)

uint16_t midscale = 0x8000;

for (uint8_t ch = 0; ch < 8; ch++) {

spi_write_reg(fd, REG_DAC_BASE + ch, midscale);

}

// 4. Trigger LDAC update via software

spi_write_reg(fd, REG_TRIGGER, 0x0010); // set LDAC to 1 4 th bit in reg 0x05

printf("All 8 channels updated to midscale (0x8000) with ×2 gain.\n");

printf("Expected VOUT ≈ 2.5 V (for 2.5 V internal reference).\n");

close(fd);

return 0;

}