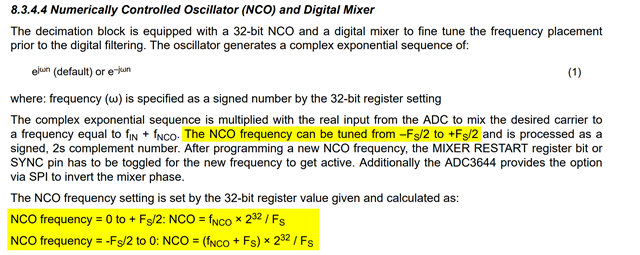

Tool/software:

Hello, I am attempting to collect parallel complex decimated data from this device and run into a problem whenever I increase the clock frequency above 500kHz.I have posted some example output plots given the following constant parameters:

NCO Frequency: 500kHz

Input frequency: 503kHz

Decimation setting: 2

Resolution: 16-bit

Note that when I say clock frequency I mean the input clock to the +/- input to the ADC3544, not DCLKIN as I am not using the serial mapper, but instead the parallel DDR data on outputs 1-16. These are plots of only the in-phase component of the complex decimated data.

This first plot I am plotting with clock frequency = 500kHz

For this plot, I am plotting every 10th value with clock frequency = 500kHz

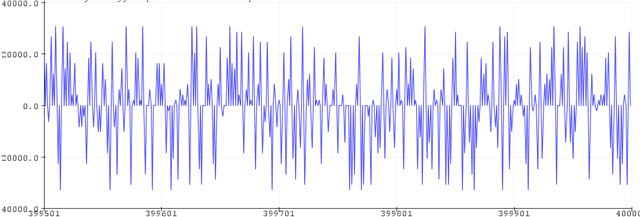

For this plot I changed to clock frequency = 550kHz and plotting every value (input waveform doesn't appear to make a difference)

These plots make me think there is something wrong with the way the data is outputted or collected, but I am not sure what could cause it to work at clock input = 500kHz but not 550kHz. If I lower the clock frequency it still appears to work. Any help would be highly appreciated. Let me know if I can clarify anything.

Felipe.