Hi,

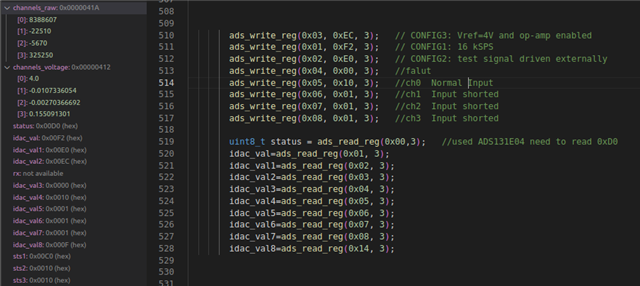

I am interfacing the ADS131E04 with my MCU through SPI. I’m following the startup sequence as per the datasheet:

Sent RESET (0x06) command

Waited for 100 ms

Sent SDATAC (0x11) command to stop continuous data mode

Attempted to read the ID register (0x00)

However, I always read back 0x00 instead of the expected 0xD0 (for ADS131E04).

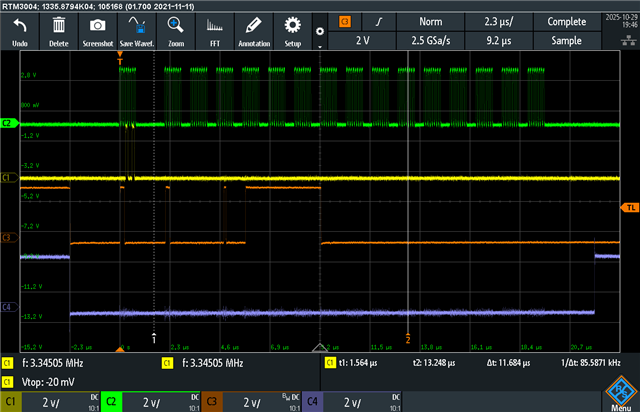

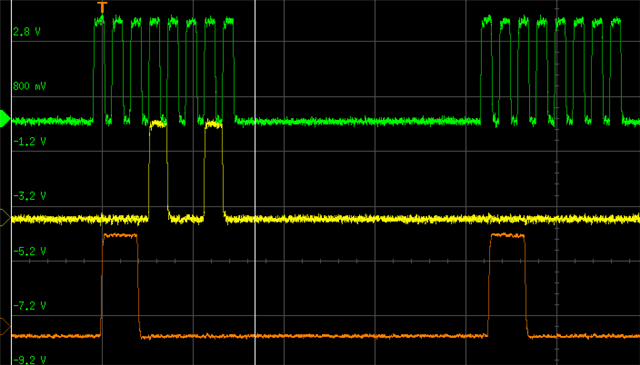

The SPI lines and MOSI data appear correct on the oscilloscope, and the first byte is transmitted properly.

Additional observations:

The MOSI first byte reflects the D0 data (both in the first and third bytes).

Sometimes, the correct 0xD0 pattern appears, but not consistently.

We tried running in all SPI modes (0 to 3), but the result remains the same.

Questions:

Is the WAKEUP (0x02) command mandatory before sending SDATAC and reading the ID register after power-up or reset?

What is the recommended delay after WAKEUP before register access?

Could improper VCAP capacitor values cause unstable SPI communication or ID read failures?

Are the VCAP, AVDD, and AVSS capacitor values required to exactly match the datasheet / EVM kit recommendations?

(Currently using either 1 µF and 10 µF capacitors for all rails.)

VCAP pins: Connected with 1 µF or 10 µF capacitors (need clarification if exact matching is mandatory).

SPI setup details:

SPI clock: 10 MHz

Verified correct MOSI data on oscilloscope

Thanks in advance for your support and guidance.

Thanks,

Manikandan V