Other Parts Discussed in Thread: MSP430F5659

I previously posted a similar question but didn’t receive a response, so I’m posting again.

I’m currently using the DAC63002 with an external reference voltage connected to the VREF pin. The DAC receives data via SPI communication from an MSP430F5659 MCU.

Under normal communication conditions, the VREF pin draws almost no current. However, when a communication error occurs, a large current flows into the VREF pin, causing the reference voltage to drop.

Here’s what I’ve observed:

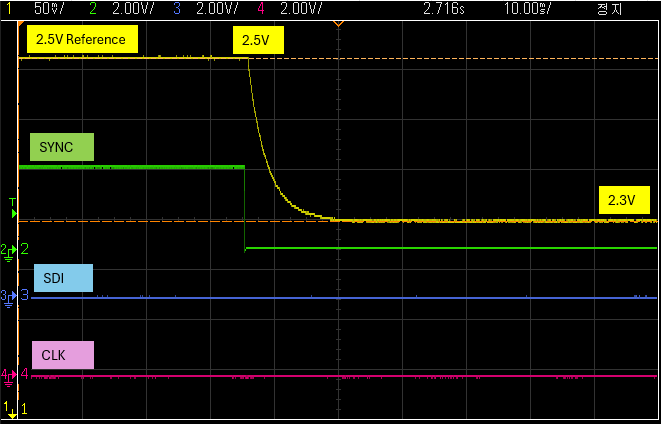

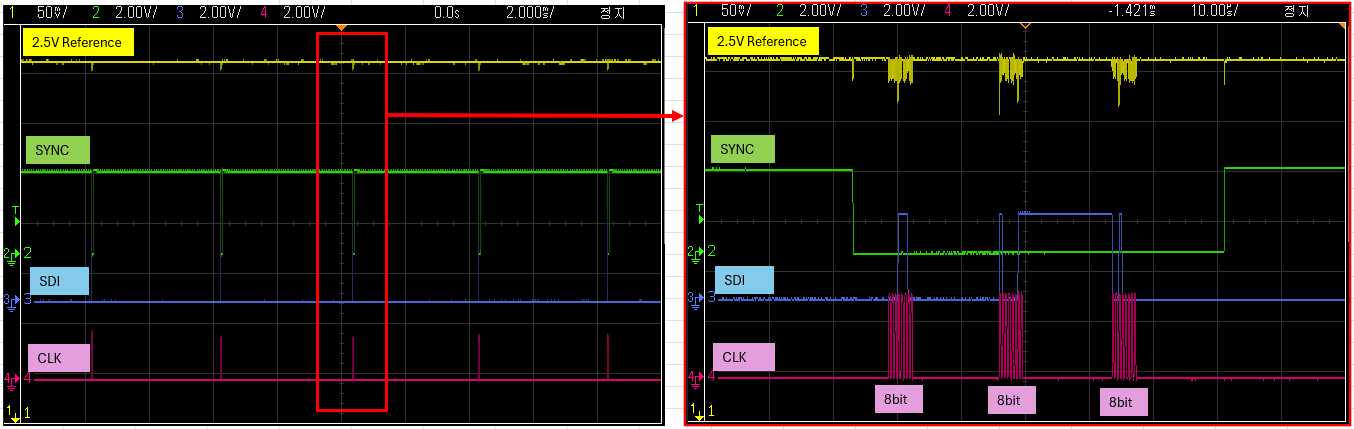

Normal operation:

The MCU sends 3 sets of 8-bit data (total 24 bits) via SPI, and the SYNC signal is closed immediately after transmission. In this case, the reference voltage remains stable, and no significant current flows into the VREF pin.

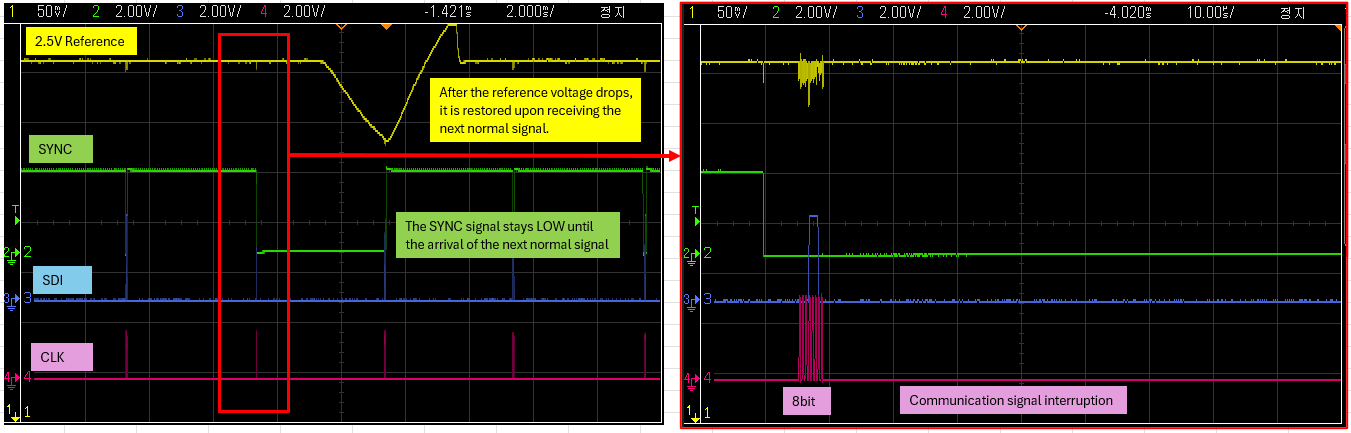

Error condition:

The transmission is interrupted after only one 8-bit data packet is sent, meaning the full data is not delivered to the DAC. During this state, the SYNC signal remains open, and a large current flows into the VREF pin, causing the reference voltage to drop. The voltage only recovers after a normal signal is received again.

My questions are:

Why does current flow into the VREF pin when a communication error occurs and the SYNC signal remains open?

Is there a way to prevent the reference voltage from dropping even if a communication error happens?

Of course, the ideal solution would be to eliminate communication errors entirely, but despite various attempts, they still occur intermittently. So I’m looking for a workaround or protective measure to ensure the VREF voltage remains stable even during such errors.

Any suggestions or insights would be greatly appreciated.

Thank you.