Part Number: TSW14J58EVM

Other Parts Discussed in Thread: ADC12QJ1600, ADC12QJ1600EVM

Dear TI team,

we are trying to readout the ADCs using the ADC12QJ1600 and TSW14J58EVM evaluation boards with JMODE8. We are using the lidar_ref_code python sofware to configure the ADC with JMODE8. Configuration looks succesfull :

There are 4 connected devices.

{'index': 0, 'flags': 2, 'type': 7, 'id': 67330065, 'location': 305, 'serial': b'FT4N0ZG8A', 'description': b'ADC12QJxx00RD A'}

{'index': 1, 'flags': 2, 'type': 7, 'id': 67330065, 'location': 306, 'serial': b'FT4N0ZG8B', 'description': b'ADC12QJxx00RD B'}

{'index': 2, 'flags': 2, 'type': 7, 'id': 67330065, 'location': 307, 'serial': b'FT4N0ZG8C', 'description': b'ADC12QJxx00RD C'}

{'index': 3, 'flags': 2, 'type': 7, 'id': 67330065, 'location': 308, 'serial': b'FT4N0ZG8D', 'description': b'ADC12QJxx00RD D'}

***************************************************************************

Initializing ADC12QJ1600 instance with defined attributes

Got Init Bit

ADC device initialization complete successfuly

ADC is ready for programming

***************************************************************************

***************************************************************************

Initializing ADC12QJ1600 instance with defined attributes

Got Init Bit

ADC device initialization complete successfuly

ADC is ready for programming

***************************************************************************

P = 2, V = 4, N = 20, FVCO = 8000000000.0

Setting the ADC's JMODE to 8

P = 2, V = 4, N = 20, FVCO = 8000000000.0

Setting the ADC's JMODE to 8

Done

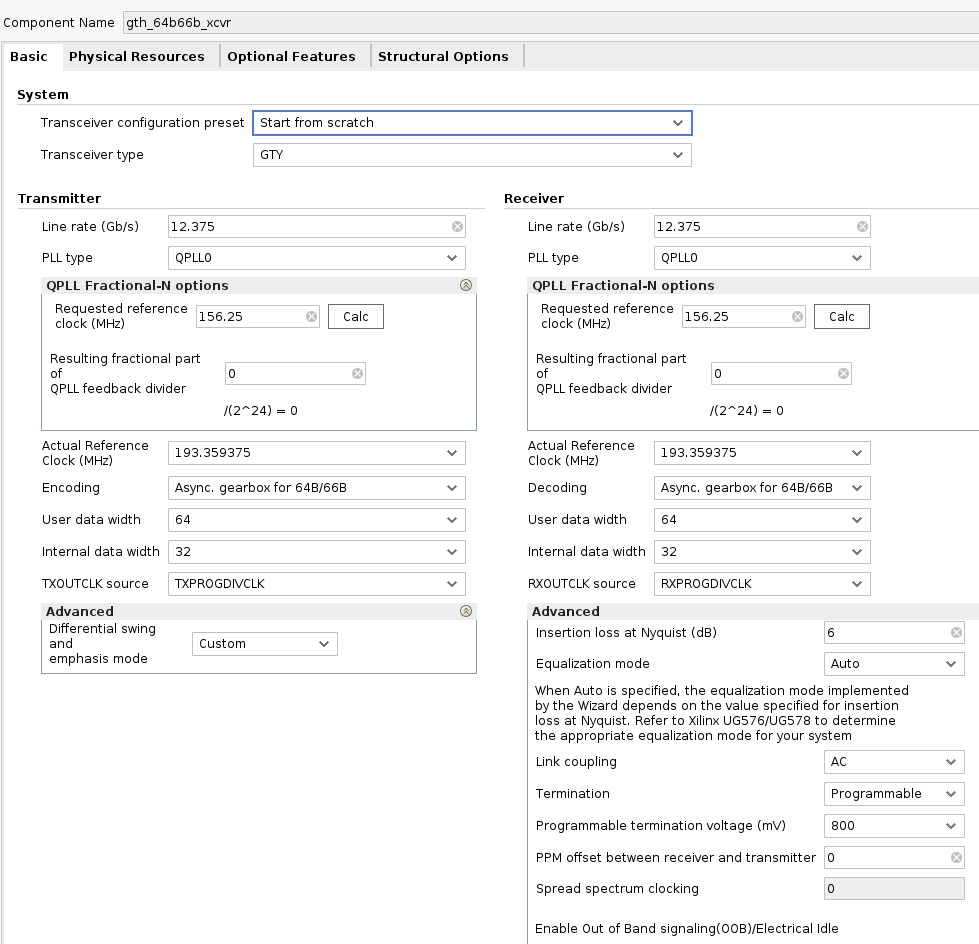

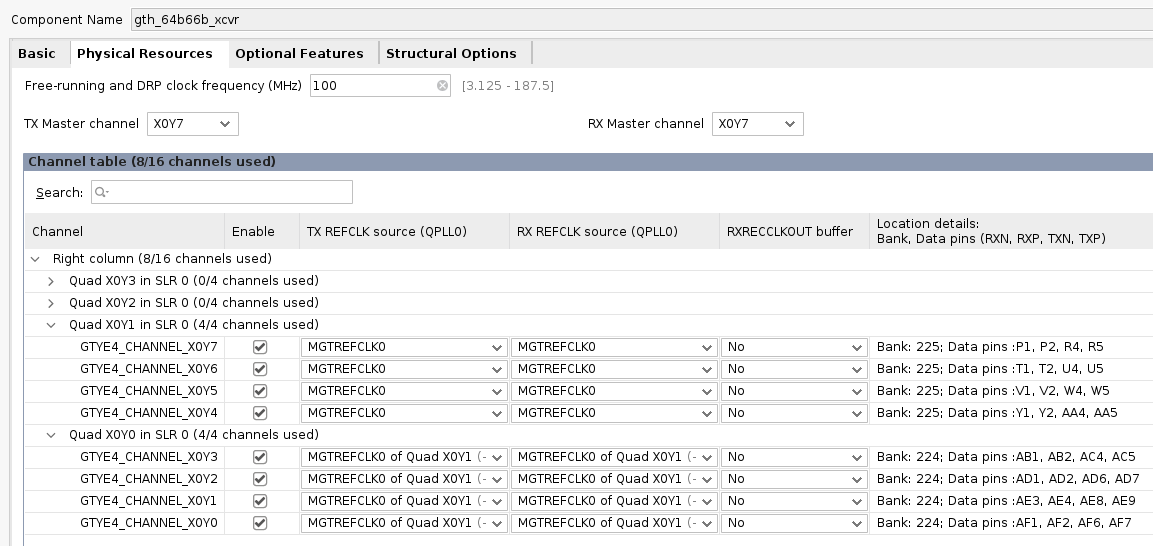

MGTs are configured for 12.375 Gbps with a reerence clock of 193.59375 MHz:

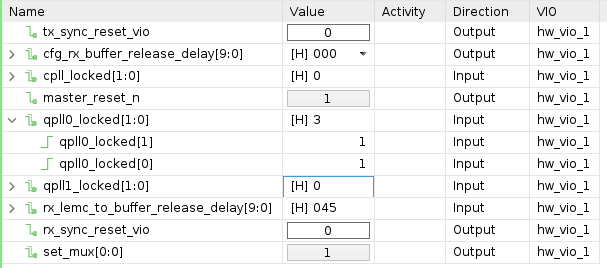

Now looking at the VIO the QPLLs are locked:

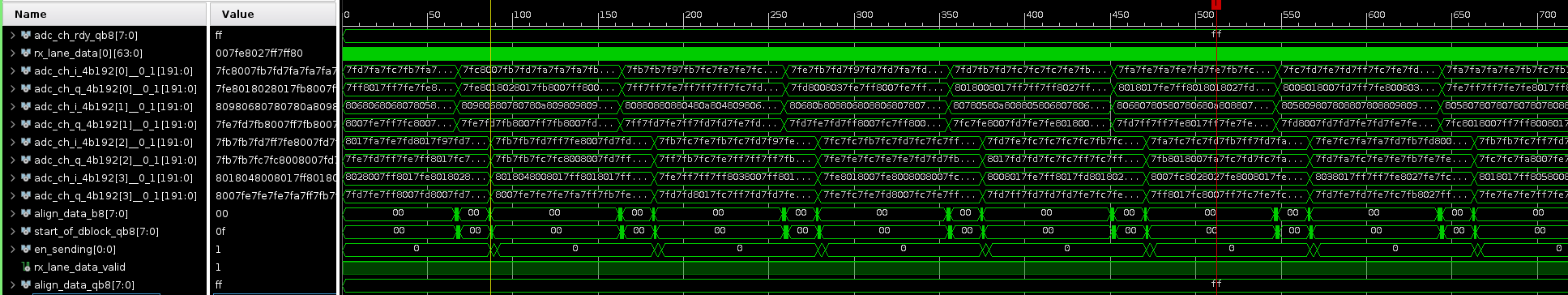

and data are coming out of the ADCs (64bits in every clock cycle) but the final vectors (adc_ch_i_4b192 and adc_ch_q_4b192) output 192 bits in every extended multiblock (ILA inside the refdesign_rx.sv):

Why we have only 192 bits in every extended multiblock? I would expect 3*32*64 bits (3 emblocks*32 multiblocks*64 bits block). We tried to plot the rx_lane_data(0) data for a 100mv peak to peak sine wave of 1 MHz and we are getting the following:

where even the amplitude is wrong. We are using the following paramemters on the gteware: IP_64B66B, ADC_RESOLUTION=12, NUMBER_OF_RX_LANES=8, NUMBER_OF_QUADS=2, RX_LANE_DATA_WIDTH=64 and RX_E_VAL=3).

For sure we are missing something important but could you please help us to solve this?

Thank you in advance,

Panos