Part Number: DAC39RF12EVM

Hi Team,

Posting on behalf of our customer.

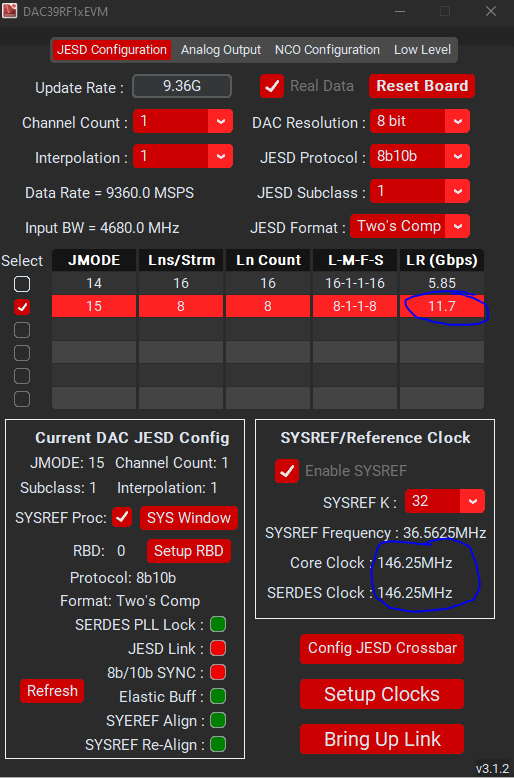

I am using the DAC39RF1xEVM GUI to setup the clocks and registers on the DAC39RF12EVM. When I follow the AMD JESD204C v4.3 LogiCORE IP Product Guide (PG242) specification document it says that for the JESD Protocol 8b10b the clock frequency should be the serial line rate divided by 40. When I try to setup a serial line rate of 11.7Gbps the Core Clock should be 292.5MHz, but your GUI seems to be setting it up as 146.25MHz. It’s essentially taking the line rate and dividing it by 80. Can you confirm that this is being setup correctly and that it will work with a Xilinx FPGA that is communicating the same line rate but operating with an FPGA clock of 292.5MHz?

Regards,

Danilo