Part Number: ADC32RF55

Hello team,

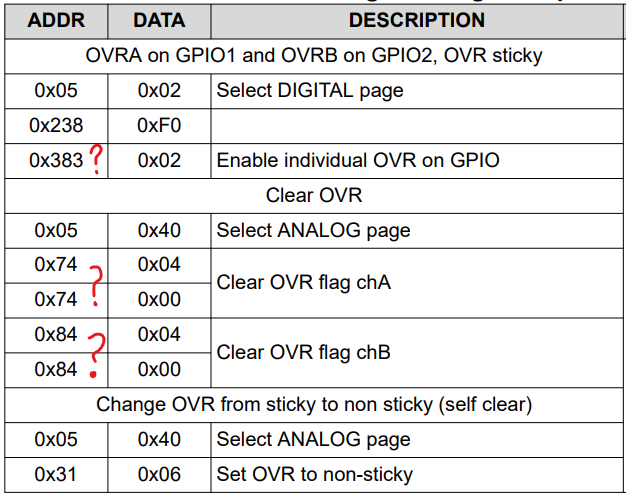

I am confused regarding the overrange (OVR) setting for ADC32RF55.

I want to confirm how to set OVR on GPIO and clear them.

I couldn't find register address 0x383, 0x74 on datasheet register map.

Also 0x84 is register for JESD PLL setting.

Would it be possible to check the correct register setting for setting OVR on GPIO and clear them?

Best Regards,

Kei Kuwahara