Part Number: ADS52J90

Dear Technical Support Team,

I aim to do simultaneous sampling with multiple ADCs(sampling timiming difference between channels within 1ns)

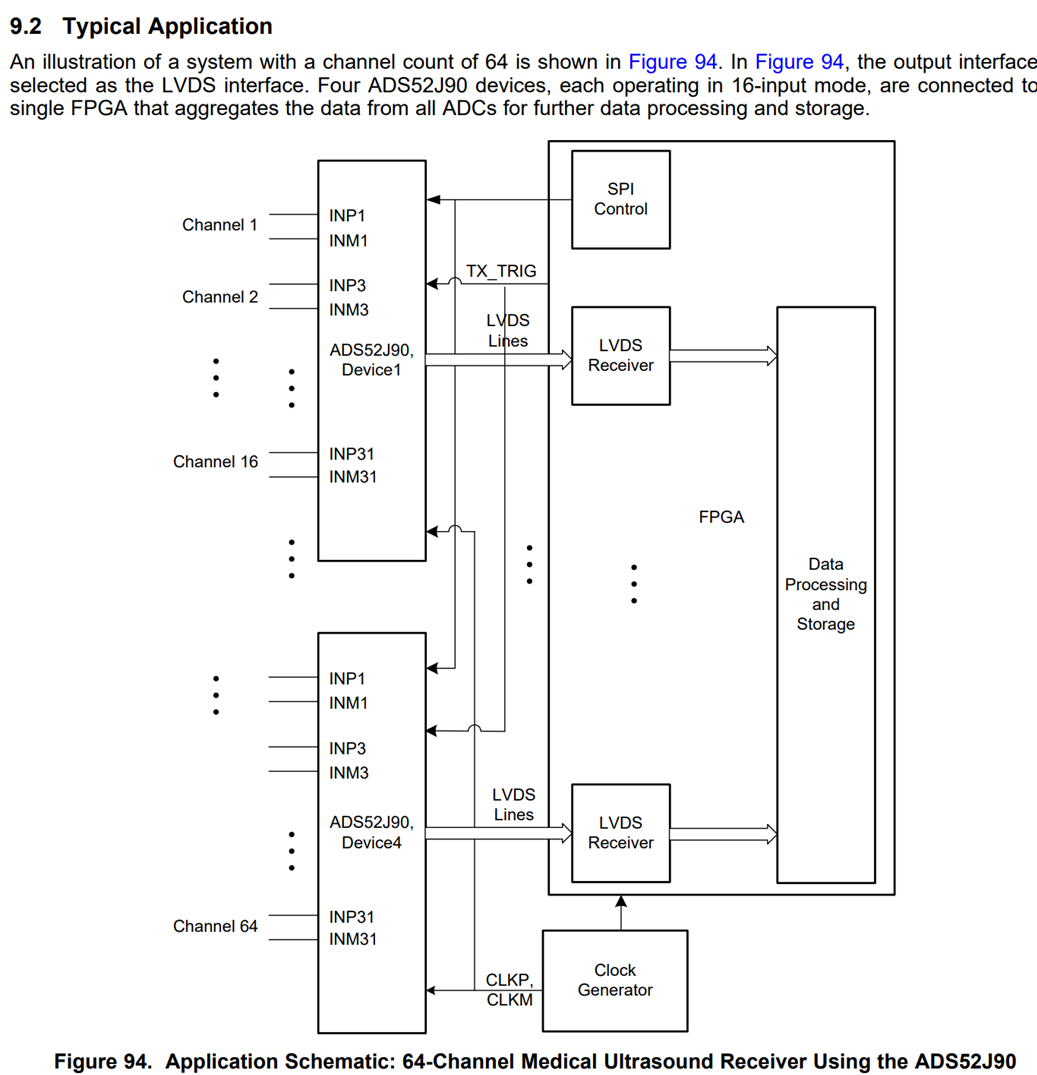

For example , datasheet has four ADS52J90(16ch) for 64ch analog input.

Q1

Can four ADS52J90 for 64ch analog input sample simultaneously?

Q2

For acheving sampling timiming difference between channels within 1ns, does the skew of four sampling clocks(CLKM/N) and four trigger signals also need to be within 1 ns?

Q3

Are there any application notes or reference designs for applications using multiple ADS52J90s, such as the one described here?

Best Regards,

ttd