Hi everyone,

Working currently with 4 ADS1282 devices, I have troubles synchronizing the ADC devices together. To make it as clear as possible, here is the set-up used:

1) Power on switching

2) SDATAC command

3) Write/read registers

4) RDATAC command

5) Taking Sync pin low

6) Taking Sync pin high (sync event)

All ADCs have the same configuration (Continuous Sync mode, 500SPS, other parameters as defaults).

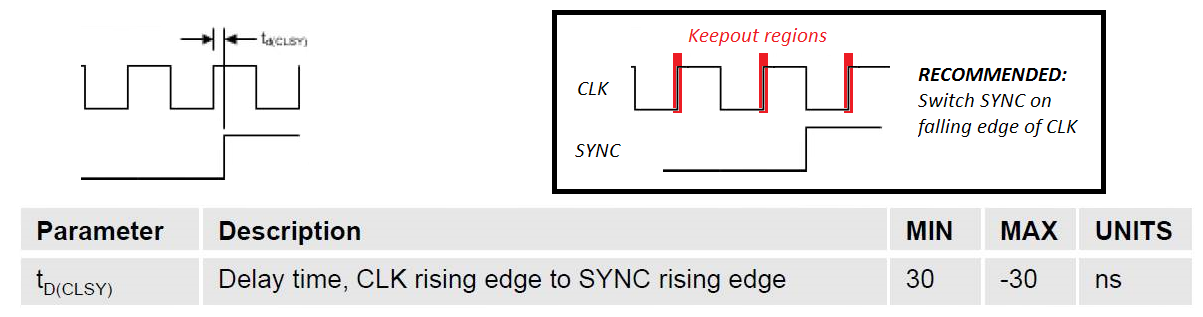

The clock, sync and reset signals are shared for a 4 ADCs. All 4 devices get the SYNC signal at the same time.

However, after 63 samples re-synchronization cycles, the drdy_n signals are not going down at the same time for the 4 ADCs, hence a small offset in the data sampling. I am then wondering if I did something wrong while configuring the ADC, or what could be the source of such a sync mismatch.

Thank for any idea you can provide.

Regards