Hello,

I am trying to sample all 8 channels of an ADS8568 simultaneously using the serial interface at 400 kSPS. Other configuration details include:

- Software mode.

- ADS8568 uses its internal clock (CCLK).

- CONVST_x generation and serial transfer logic is clocked independently of the ADS8568’s CCLK (in other words CONVST_x is generated asynchronously from the perspective of the ADS8568).

- All CONVST_x inputs are electrically tied together, because I want as close to simultaneous sampling on all 8 channels as possible.

Has anyone had success using the ADS8568 in this way?

Some more details:

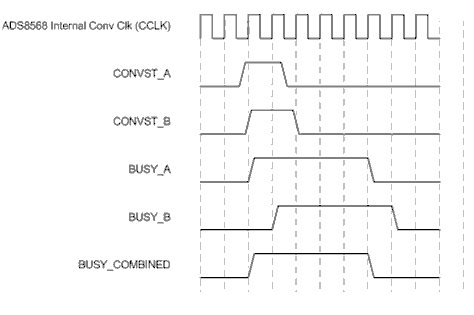

I think that my issue relates to CONVST_x setup time and the BUSY/INT pin’s functionality. If all CONVST_x inputs are electrically tied together and generated by a clock that is asynchronous to the ADS8568’s internal clock, then there will be times that some of the CONVST_x inputs make setup time while others don’t. The following diagram visualizes this behavior:

In the above diagram, CONVST_A and CONVST_B are electrically connected to the same driver, but because of the electrical characteristics of the board, CONVST_A has made setup time while CONVST_B has not. When this happens, the SAR ADC module for channel pair A goes “BUSY” one cycle before the SAR ADC module for channel pair B. Then the ADS8568 combines the two BUSY signals to form one BUSY output according the following rules:

“This pin transitions high when a conversion has been started and transitions low for a single conversion clock cycle (tCCLK) whenever a channel pair conversion is completed and stays low when the conversion of the last channel pair has completed.”

When this happens, the combined “BUSY” output drops at the appropriate time for the channel pair who’s CONVST_x made setup time, which is one cycle too early for the channel pair that failed setup time. If I perform a serial transfer as soon as I see BUSY drop, I will get the newly sampled value for the channel pair that made timing and a repeat of the previously sampled value for the channel pair that failed CONVST_x setup time. This results in a 6 bit ENOB!

I have verified that simply waiting an additional ADS8568 internal conversion clock cycle after BUSY drops before performing the serial transfer resolves the issue, but this takes approximately an additional 90ns, which there is no room for in the extremely tight 400 kSPS serial timeline. Since the ADS8568 advertises simultaneous high-speed signal acquisition of up to 400 kSPS in serial mode, I assume that there is a way to get around this. My question is how?

Note that the provided example where CONVST_A makes setup time and CONVST_B doesn’t is just one case of many and with the same physical setup it is possible for CONVST_B to make setup time while CONVST_A fails.

Thanks in advance for the responses!

Chuck