Greetings,

I'm trying to acquire data using two ADS1258 on a shared SPI bus. I can communicate to both chips without problems and so I configured both ICs to convert in AUTOSCAN mode two channels each. The start pin is tied to high so the ADCs are constantly converting and each time that I need data I wait for the DRDY interrupt and then read the data with the CHANNEL_DATA_READ_COMMAND as recommended for a shared spi bus by the data sheet.

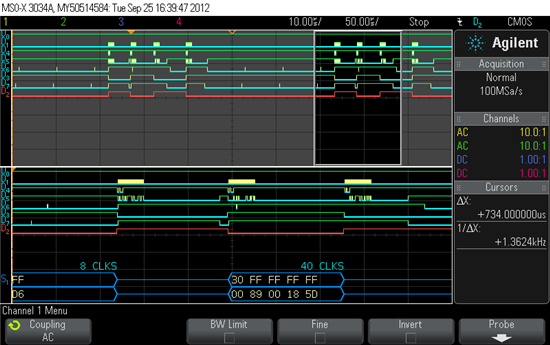

When reading the CS is just low for one of the ADCs but non the less the DRDY lines for both ADCs immediately assert high. This kind of behavior is not documented in the data sheet and as I need the line signals to identify what ADC I have to read from, this behavior is quite annoying. Hence I would like to understand if I'm dong something wrong here or if this kind of behavior is documented somewhere and I just missed it.

The following image shows the communication the bus. In the following I explain the signals in the graphic in order of their appearance:

D0=PWR_ENABLE;

D1=SPI_CLK;

D4=MOSI;

D5=MISO;

D6=DRDY_ADC1;

D3=CS_ADC1;

D7=DRDY_ADC2;

D2=CS_ADC2;

Thank you for you input and consideration,

Gunter Kanitz