Hi everyone,

I have a DAC8581EVM board with a DAC8581 unit. I have designed an VHDL interface on a FPGA in order to introduce the SPI data. When I connect the development board with the FPGA and the power supplies, I get a wrong output voltage.

Here are the connections I have implemented:

ANALOG POWER SUPPLIES

=======================

Vcc <= +11.70 V (to AGND)

Vss <= -11.70 V (to AGND)

AVdd <= +5.10 V (to AGND)

AVss <= -5.10V (to AGND)

AGND <= AGND

DIGITAL POWER SUPPLIES

=======================

+5VD <= +5.10V (to DGND)

+3VD <= +3.3V (to DGND)

DGND <= AGND

DAC DATA (J2)

============

J2-1 <= CSn;

J2-3 <= SCLK

J2-11 <= SDIN

J2-14 <= CLRn

When SDIN <= "4000", the output voltage at TP5 = 3.5 V, but the datasheet indicates that it should be 2.5V. With other values there are discrepacies too, as shown in the table below:

SDI Value Expected value Obtained value Error

============ ============ =========== ====

0x7FFF 5V 4,02V 19,6%

0x4000 2,5V 3,49V 39,6

0x0000 0V 0V 0%

0xC000 -2,5V -2,2V 12%

0x8000 -5V -4,6V 8%

I expected that a 16-bit DAC should be more accurate, so I think that I am doing something wrong. If so, this mistake could be in the connection, or in the data transfer.

- Connections are explained above.

- Jumpers : all the jumpers are set as the default implementation (datasheet).

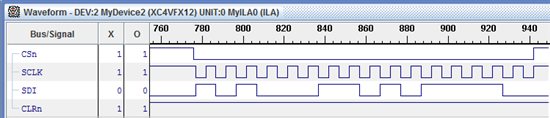

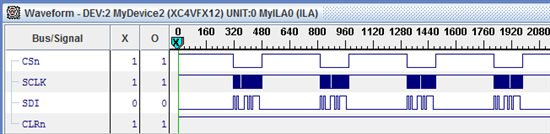

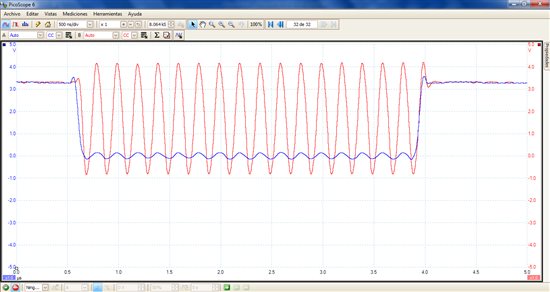

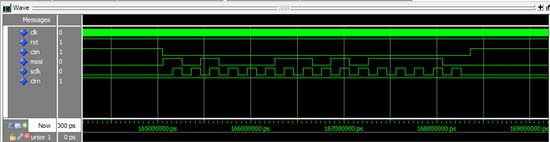

-Below there is a graphic to show the SPI Data transfer through SDI pin. The data trasnferred is A35E hex.

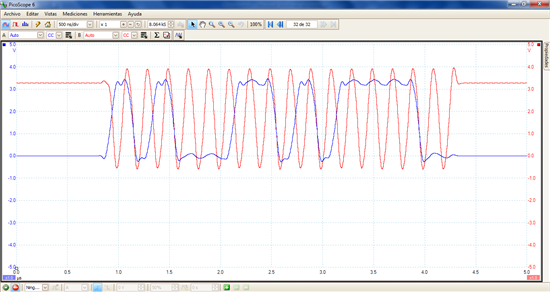

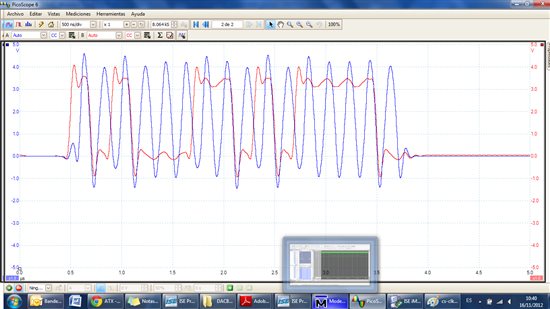

with SCLK frequency = 10 MHz. Below a multiple conversion is performed (the SDI data is always the same), sending data @ 200 Ksamples/s:

If anybody has worked with this DAC, or can help with the information given and the DAC datasheet, I would be very grateful for your help. If any additional information is needed, just ask.

Thank you everybody in advance,

Alberto