Other Parts Discussed in Thread: ADS5485

Hi Team,

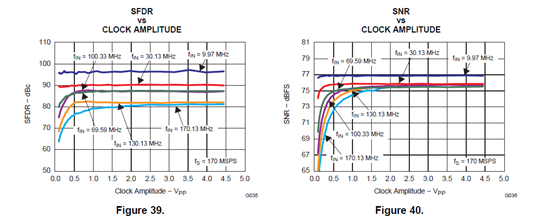

The ADS5485 is being used at 200 MHz. The differential clk amplitude is only 1.0Vpp. (Notice that this is below the recommended 1.5Vpp min)

What are the tradeoffs to having the differential clk amplitude set to 1.0Vpp as opposed to 1.5Vpp?

Over temperature, what is the absolute min that the clock Vpp must drive?

Best regards,

Brian Gosselin