Hi,

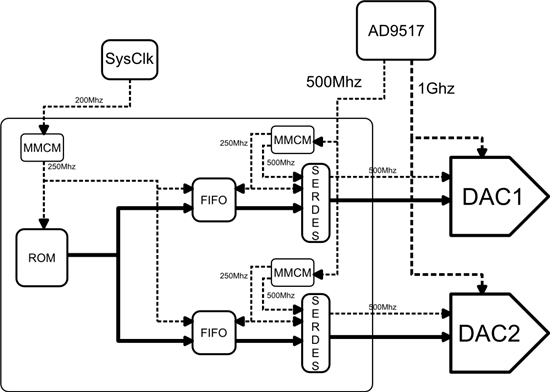

I'm currently working with Virtex-6 ML605 and 2xDAC5681z at 1GSPS.

I finally could configure both DAC properly. So, I designed this data flow, in order to evaluate the system. My original system will work with data frames instead of stored frames, so I need to provide a continuous data flow.

As you can see, I read a signal stored in a ROM with FPGA clock. Then I send the data to another clock domains through some asynchronous FIFO.

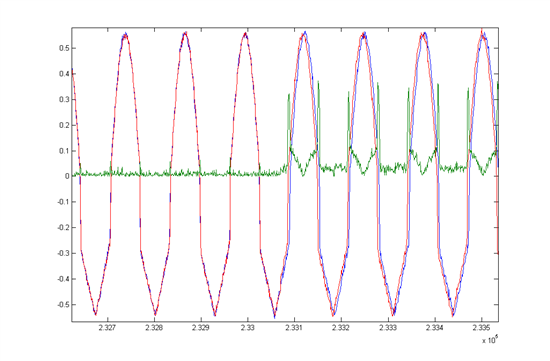

By using an oscilloscope, I observed that this signal is showed with the proper tension level, but every now and again something happend in time domain.

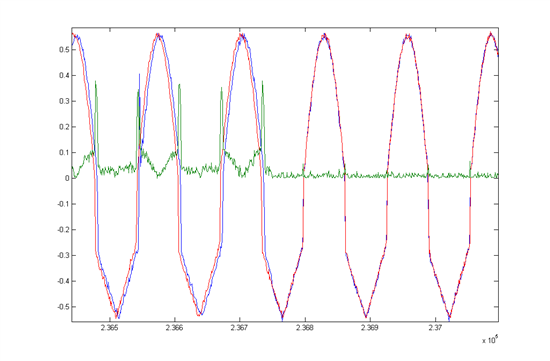

In this another captured picture, both DAC are synchronized, but in some moment, one of the DACs some samples are losing, and signals are desynchronized.After some small random period, some samples are losing in the other DAC, as you can see at this other picture.

I was thinking about it, and I decided to generate 2 ROMS and read with each of DAC clock. At that time, desynchronize problem disappears.

As far as I understand, all of these created clocks couldn't not be the same. I mean, maybe one has 249.99Mhz, and the other one has 250.01 Mhz, and this can produce that FIFO pointers can cross.

I was looking up some solution for this problem. The best option I found was, reset from time to time, in order to avoid this cross pointers.

I tried this option, but the problem didn't solve.

Do you have any idea that how I can solve this problem?

Thanks

Regards,

Jose Correcher