Hello,

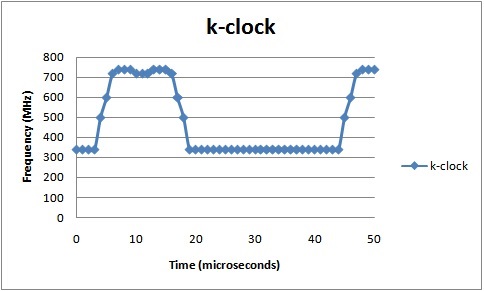

I'm developing a data acquisition system for a swept source optical coherence tomography system. I would prefer to directly sample of the k-clock to avoid the processing step of re-sampling the data. My k-clock will be frequency varying over time from approximately 340 MHz to 740 MHz. The frequency vs. time behavior is roughly shown in the figure below.

I would like to know if it is possible to use this type of signal (provided it meets other electrical specifications) as the sample clock input for the ADC08D1020. I suspect the relevant clock specifications are minimum frequency (200 MHZ per datasheet), maximum frequency (1 GHz) and clock duty cycle (20%-80%). This makes me think I should be able to use this ADC chip, but I would appreciate any help or thoughts on the matter. Are there other important clock specifications to be aware of for this sort of sampling?

Thank you for your time. I am happy to discuss in further detail or elaborate if necessary.

-richard