Team,

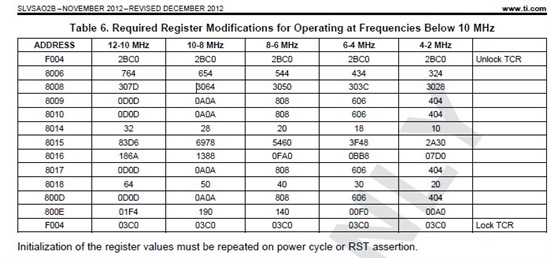

I’m not having much luck communicating and am about 90% sure it has to do with clock rates. From the datasheet I know the chip takes two clock signals, SCK (SPI input clock), and FCLK (flash clock). I know the max frequencies are 10 MHz and 12 MHz respectively, and that the flash clock to SPI clock ratio must be 6/5 or higher. The datasheet also states that “operation below 10 MHz acceptable."

So the questions I have are:

1) Is the 10 MHz lower operating limit for SCK or for FCLK?

2) what are the absolute min SPI clock and flash clock frequencies, and what sort of config changes are required?

Thanks,

Ryan