Hi,

I'm using an ADS8344 in external clock mode, no power-down between conversions.

It seems the very first control bits after power-up of the device are not followed by a correct conversion output.

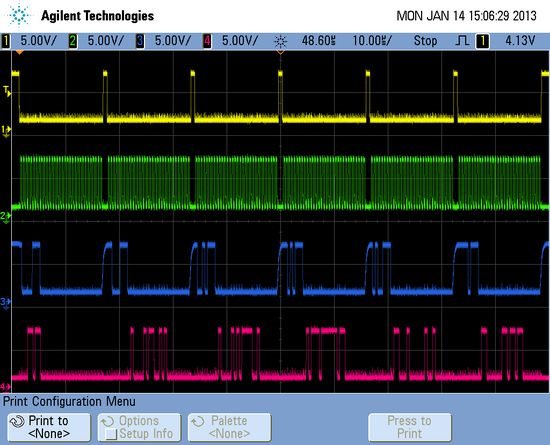

On the image above DOUT is the red channel at the bottom, DIN the blue one, DCLK the green one and the yellow trace is CS.

As we can see, DOUT output some bits even when receiving the first control sequence (channel 0) on DIN, then it seems there is only zeroes as the conversion result. The next control bits (channel 1) are followed by the correct conversion value on DOUT. All next channels are correctly converted.

Is it due to a clock mode change because the ADS8344 was in internal clock mode at power-up? The datasheet doesn't seem to mention which mode is selected by default at power-up.

Thanks in advance for any comment.

Regards,

Eric.