Other Parts Discussed in Thread: ADS1147

Hi all,

First, I'm very sorry for my English.

And the second,

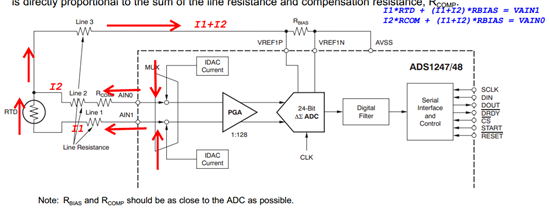

In the accordance with the Three-Wire RTD Application with Hardware Compensation of SBAA180 of ADS1147(see below), the red line was marked is the direction of current, and use the RBIAS to produce external reference voltage.

My setting as follow:

The NTC range is 3.75KΩ to 52.3K

RCOM: 30K

RBIAS: 15K because I want to use external reference voltage of 1.5V

AVDD: 3V

AVSS: 0V

PGA: 1

IDAC(AIN0,AIN1): 50μA

Data rate: 5sps

The problem is: when the resistance value of NTC less than 30K,the external reference voltage is kept at about 1.5V, this is acceptable.But when the NTC value greater than 30K.the reference had droped severely,such as 1.2V, 1.07V and so on.Can you tell me something wrong about my schematic,setting and why the IDAC can fall.

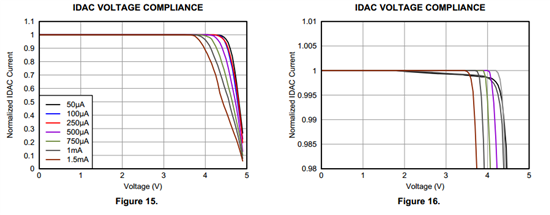

By the way,can you explain Figure 15 and 16 for me? The voltage means what? AVDD or others?

Penn