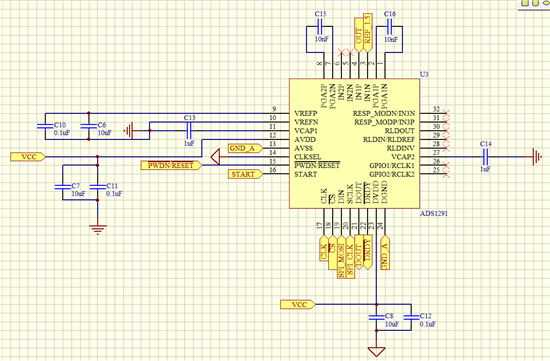

hello everyone. I have a problem about ADS1291. Here is my circuit plot

I use the Single-end Input. The input of IN1P is the ouput of an instrument amplifer and the common voltage is 1.5V

and i use the same VCC which is 3V for AVDD and DVDD.

and the same GND for AVSS and DGND.

and i connect the rest pins to a msp430F5522.

But somehow i can't read the correct output .

i already check the analog amplifer is fine so the input of INIP is fine.

so i am not sure is there something wrong with my ADS1291 circuit or my MSP430 Firmware.

anyone please help me check out my ADS1291 Circuit?

thanks a lot