HI all,

I have an acquisition system based on ADS1258, utilizing 8 of its channels in the single ended mode. The problem I am facing is i am getting a constant error value every other time, say for example, I finish reading all 8 channels the first time, it is all comming correctly, the second round of reading returns a constant error value (different for individual channels) and this loops. Here is how I am initializing the register

CONFIG0 = Fixed channel mode | SPI_RST 256

CONFIG1 = Idle mode sleep | Delay (0) | Data rate (2)

GPIOC = 0x00

GPIOD = 0xFF

MUXDIF = 0x00

MUXSCH = 0x00

MUXSG0 = 0xFF

MUXSG1 = 0x00

SYSRED = 0x00

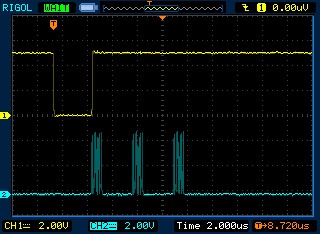

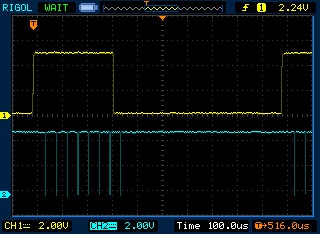

My SPI runs at 4.5MHz and seems to be running ok as seen in the waveforms acquired from my oscilloscope.

CH1: DRDY

CH2: SPICLK

CH1: START (conversion)

CH2: DRDY

My code goes like this. A timer is set to be triggered every 1mS at which the ISR raises the START conversion line. I then receive conversion completion through EXTI interrupts since the DRDY lines are connected to my controller so as to generate EXTI interrupt. After receiving the 7th sample in a batch I lower the START conversion line. After receiving the 8th sample I send the whole batch to my PC through USB. A new cycle starts when the timer is triggered after 1mS. Now what are the odds that I receive a constant error value for all channels in every other batch? I walked through my code for blunders but it is quite simple to make any (I mean I didn't find any!). Since I am reading in channel data read direct mode, I have made sure that enough time elapses between two channel read operations.