Hi,

Two questions about DAC5674 (http://www.ti.com/product/DAC5674#relprod)

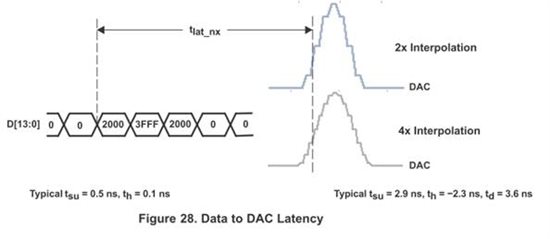

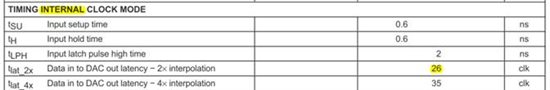

- The “Data to DAC latency”( tlat_nx, see below figure from DAC5674 datasheet) is not a fixed value, according to datasheet, the typical latency in 2X mode is 26 clock cycles from D[13:0] input.

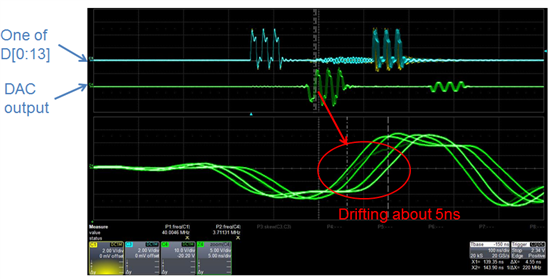

Below is my measurement, the average latency time is indeed about 26 clock cycles(at 200 MSPS, a clock time is 5ns, and 26 clock cycles is about 125ns). But, the latency is not a fix value, drifting about 5ns.

The time deviation of DAC output is not acceptable in my application, and I am also wondering that is a 5ns output time deviation normal in a 200MSPS DAC (a clock cycle deviation)?

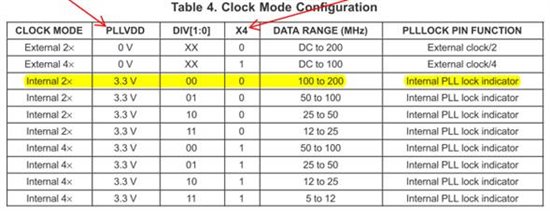

Is there any suggestion to improve the time deviation ? - DAC5674 setting on my PCB is as the yellow line below :

And the clock input frequency on CLK/CLKC pins is 200MHz.

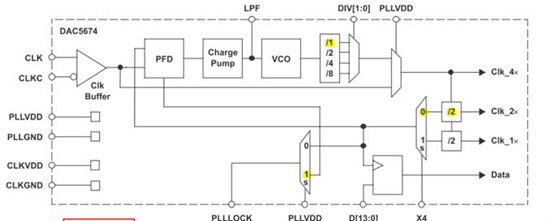

My question is : what is the clock frequency of Clk_2x ? This should be the clock rate to clock in the input data from D[13:0].

Thanks a lot !