Other Parts Discussed in Thread: ADS131E06

Hi,

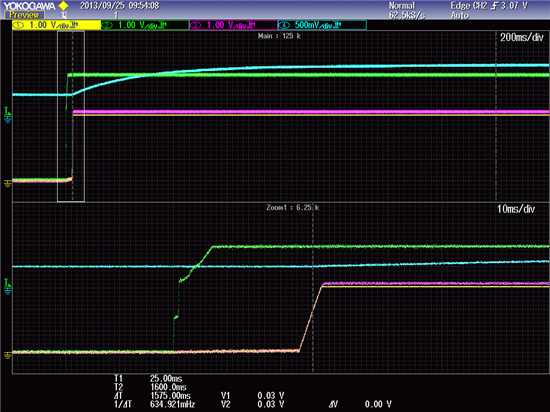

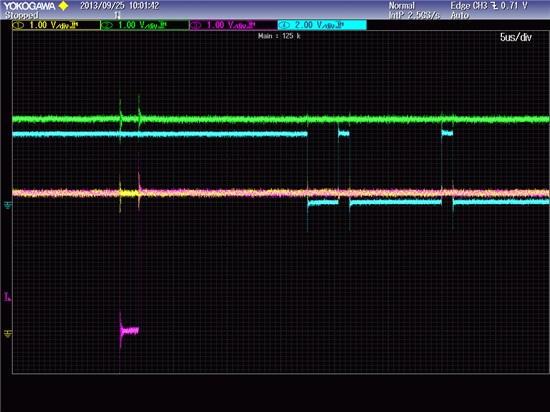

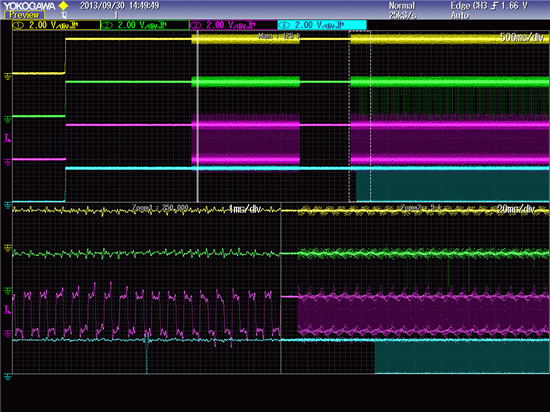

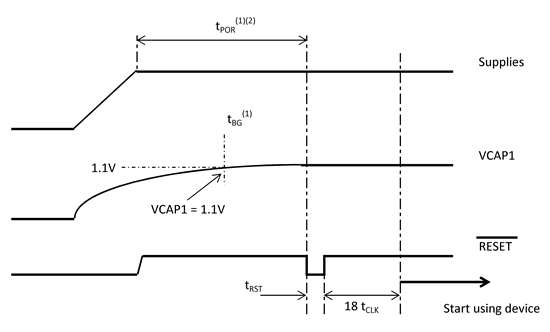

i do have a problem with a board containing multiple ADS131E06 ADC's. The board contains an FPGA, controlling 6 ADS131E06 ADC's. Each ADC has a separate SPI bus to the FPGA. In the FPGA, 6 identical SPI blocks (state machines) control the init and running of the ADC's. As the board is powered, first the FPGA is configured. After this configuration, the FPGA initializes the ADC's. The problem we're facing is that the first time the FPGA initializes the ADC's, on of the ADC's (always the same) won't work. If the FPGA is then configured again, with the same bitfile, all ADC's initialize properly. I have checked the SPI timing against datasheet timing diagrams, including power supply sequencing. I can't see any problems there. Also signals look clean and tight. I also compared the malfunctioning ADC with another ADC on the board. I can't see any timing differences there. I also checked rise-times of the power supplies, reset signals, etc. I also tried changing (lowering) the drive-strength of the FPGA . No luck there either. Do you have any suggestions or clues were to look?

Kind regards,