I'm trying to set up the ADS 1247 per figure 51 in the data sheet.

My setup mostly uses the defaults except for setting it to 2000SPS and turning on the internal refcon.

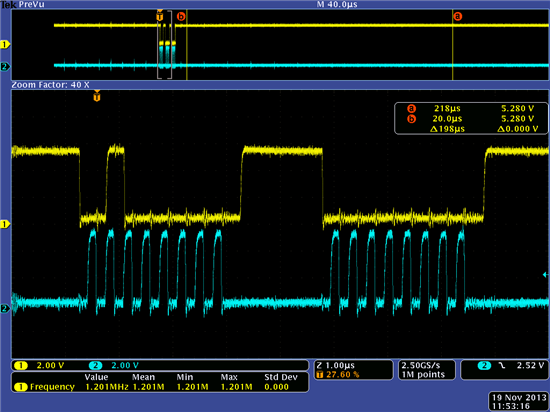

I am getting interrupts on my uController at 2K as DRDY goes low.

If I do 3 8bit block bursts (spi configured to 8 bits) with the write data as NOP (0xFF), then it runs merrily along.

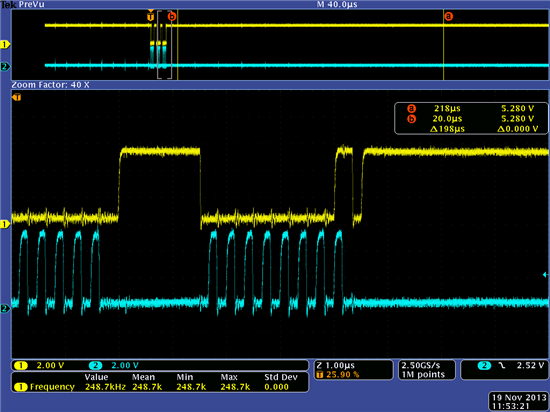

But, if instead I set the write bits to switch MUX to the other channel, Its a long time before I get the next DRDY.

My write is

0x40 0x0 0x01

or

0x40 0x0 0x13

So... when I get the the interrupt, I drop CS, write the 3 values (the first 2 reads in parallel with the writes should be my 16 bit sample), raise CS.

I see DRDY rise on the first write but its a long time till it goes down again, not .513 ms

ideas?