Hi,

I am using the EVB for the ADC12D1800RF, and noticed a problem with the HD3 performance:

sampling rate is 1800MSPS, with test signal at 124MHz.

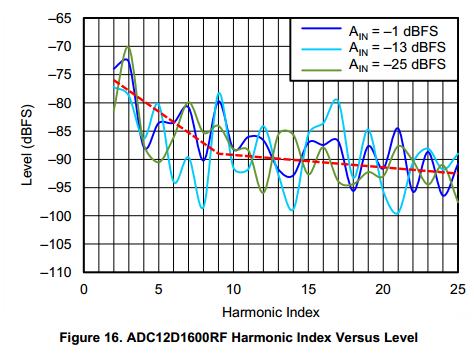

when signal level is -1dBFS, the HD3 is about -70dBC (after I perform calibration).

when signal level is lowered to -25dBFS, the HD3 becomes -50dBFS, meaning it still has about same power, despite of the signal power reduction.

same thing happened when I changed signal frequency to 248MHz etc.

note that I'm using the EVB along with the balun EVB (that has 1:2 transformer+100ohm resistor on it), with external DC-Blocks.

can you explain this odd HD3 behaviour?