Hi

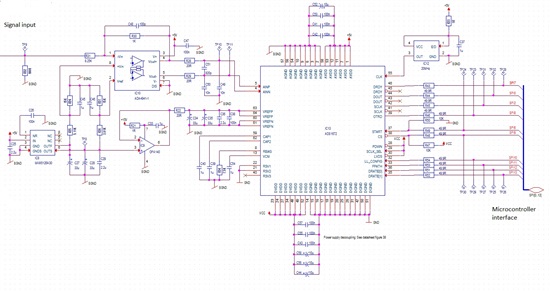

In one of our new designs, we are using the ADS1672 ADC.

When we toogle the start pin, we can get one fine ADC value, but when we hold the start pin high to make it free running, the output looks wrong.

We use an external sclk and SCLK_SEL = 1

Other setup parameters:

LL_config = 0

FPATH = 1

CS = 0

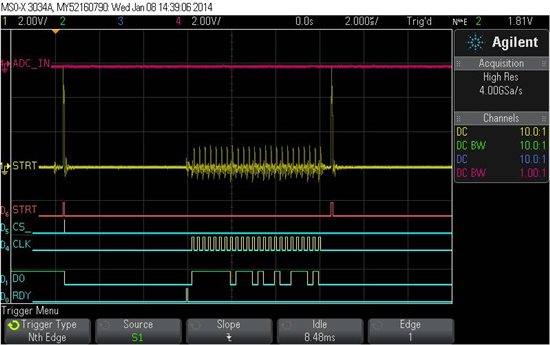

Here is an picture of a single adc measurement (start toggle) where the Dout is OK:

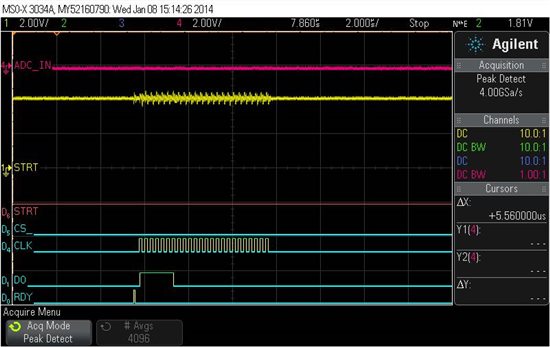

And here is a picture of the free running mode (start held high), where Dout is not ok:

Any ideas of why we can make good measurements when toggling the start pin, but not in free running mode?