I'm using the ADS5263 to digitize CCD outputs, which essentially look like square waves. The ADS5263 is sampling continuously at 100 MHz, 16 bits (not using the special CCD clamping mode of the ADS5263), and is driven by a fully differential amplifier. I noticed low frequency (~ 25 Hz), low amplitude (a few DN) banding in some of the captured images, and I've been hunting for the cause.

The best description of the glitches I can come up with so far is that certain bands of the ADC's range are suddenly shifting by a few DN with a frequency of about 25 Hz, but at random intervals. I show plots below of some of the scenarios. Each sample is separated in time by 4 ms to better show this low frequency phenomenon.

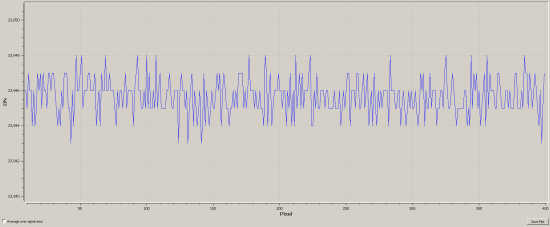

First: the ADC with a DC input. This clean, low noise, and well-behaved. The glitches only seem to occur if the ADC is seeing a dynamic input (square wave).

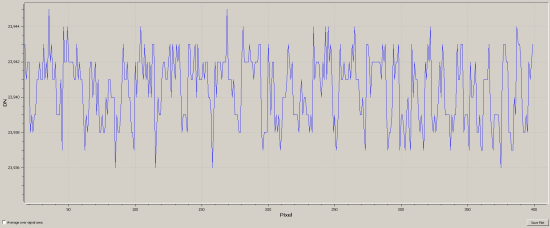

Next is the plot from a 100 kHz square wave. The square wave was generated with ultra low noise 20 bit DACs. These samples are just from one side of the square wave, which was chosen to be at the same level as the previous DC plot. You can see the odd few-DN pattern. Note that samples from the other pedestal of the square wave don't show this pattern.

Here is the same plot as above, but averaged over many samples to reduce the intrinsic ADC noise and better show the pattern:

The above plots were taken with samples around 23940 DN. Here is another averaged noise pattern from closer to the edge of the ADC range (58580 DN). The magnitude of the error seems to increase away from midband, it's about 8 DN at this level:

These glitches come and go as you move up and down the ADC range. For instance, I found that the glitches appeared from 23828 to 24075, and 27675 to 28060, but were absent in other ranges.

I've ruled out some culprits:

- It's not from the square wave generator. This same patterns appear with 3 completely different waveform generators.

- It's not from the FPGA in the system that captures the data - the linear ramp mode from the ADS5263 shows no glitches in acquired data.

- It shows up on multiple channels of several different ADS5263s (not just one bad part).

- It's not missing bits - I can move the glitching level up and down by fractions of a DN with the 20 bit DACs, and the glitch pattern follows up and down with an unchanged glitch magnitude.

On to my questions:

- Has anybody else seen this behavior?

- On the datasheet it shows pins 54 and 55 as no connect, but on the evaluation board it labels them REFT and REFB and bypasses them with 0.uF - possible culprit?

I'm considering ways to test for this behavior on the ADS5263EVM. It's made difficult by the limited capture capabilities of the TSW1250 (64k samples) I have since these glitches happen over long time periods. I may have to buy the TSW1400 to test this route.

Thanks in advance for any help!

-Greg