Hello,

I am using the DDC112 in a photoelectric measurement circuit but am experiencing an issue with what appears to be the DValid line. Every now and again (say 1-30) system power ups, the DValid line never appears to trigger. Looking at all of the lines on a scope (Dvalid, Dout, Dxmit, DCLk, CONV) they all seem to meet every requirement when they work (the other 29-30 times), but when it doesn't come up correctly I only see the CONV signal cycling with all of the other lines silent.

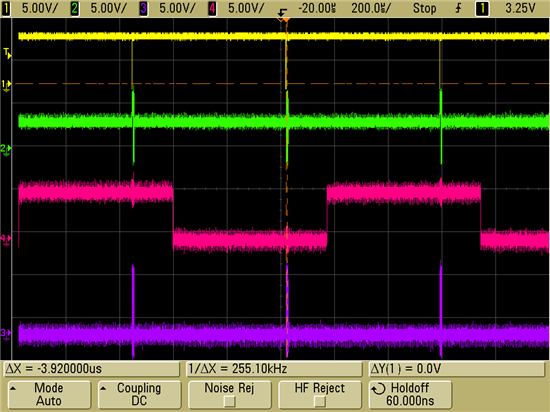

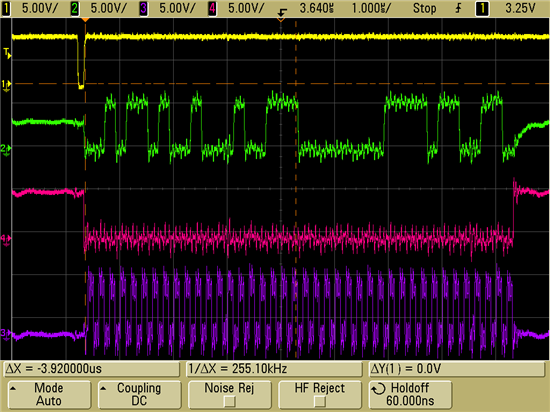

I have attached two screenshots depicting the waveforms seen when the chip is working as expected.