Hi,

New forum user, so forgive me if this is in the wrong place. I am attempting to use a PIC 18F4550 to communicate with a DAC6574IDGSG4 via I2C, I am able to send the address to the chip at 400kbs, and it replies with an ACK, but then doesn't release the SDA line. The line remains low, and the only way I can release it is to power off the circuit. If I run it without the DAC, all the bytes can be seen in the analyser, so it must be the DAC at fault.

According to the datasheet: When the bus is idle, both SDA and SCL lines are pulled high.

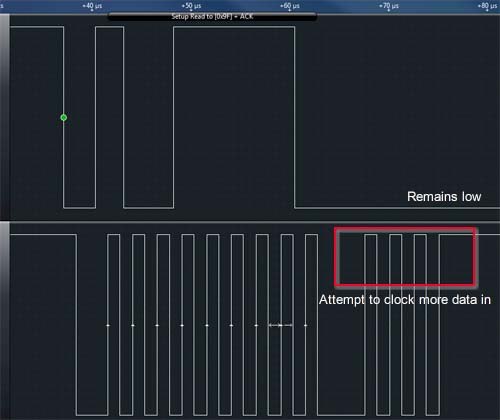

You can see from the attached Saleae Logic diagram, further data is attempted to be clocked in, and the clock runs, but as the SDA line is held low by the DAC (the 18f4550 is open drain), no data is present.

This is the second chip I have tried, and they both exhibit the same problem. I do have 4k7 pull ups, and have tried 1k pull ups and various PSU decoupling caps with no success.

Any help is most appreciated.