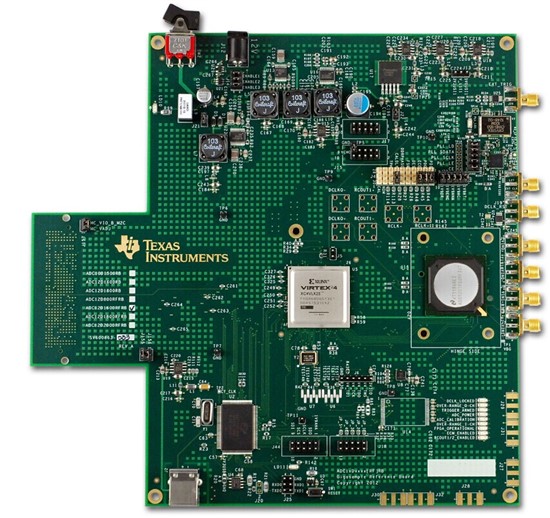

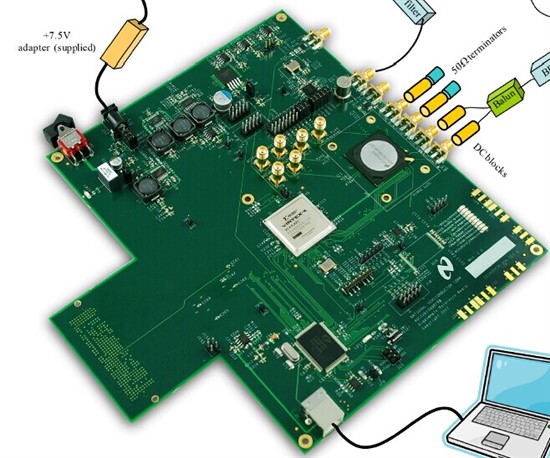

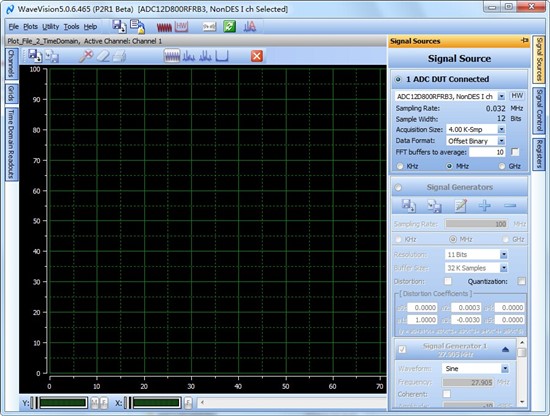

I installed the WV5 software, and followed the user guide to setup the reference board , the software successfully recognized the board, but Why the DCLK_LOCKED LED is not lit? And after clicking the capturing data button on the WV5, there is no data display and warning will come out in about 3 minutes.

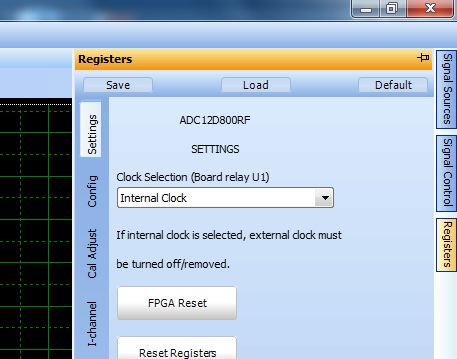

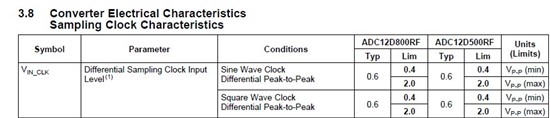

I have test the input clock to the ADC, it is normal 800MHz. I wonder whether the version of software is not right or some jumpers on the board are needed to configure or some other reasons.