Hello,

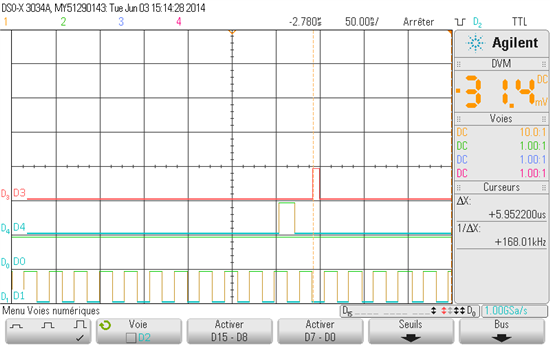

My config use 2 ADS8319, I met 2 issues type, not all parts are concerned, only some time to time (about 20%):

1) busy indicator in first position in daisy chaine is not at the correct place related to clk (it appear at low level of clk between falling edge and rising edge clk - any other clock are present in the design) (see D3 on next picture

info:

D1 = Clk, D3 = SDO (1st part)

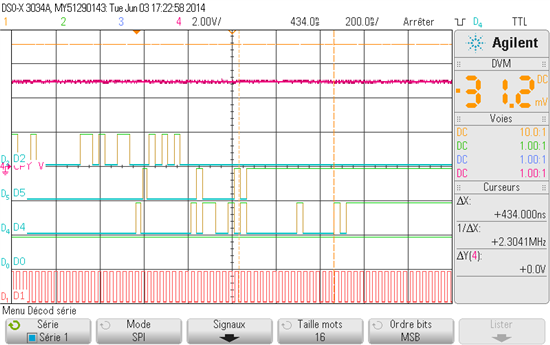

2) the number of bit transfered from the first part to the second one is greater than the 16 bits expected (1 more bit) so all conversions are improperly read (see next picture - Busy indicator of 1st part seems to be read as data by the 2nd part !!)

Other info:

D1 = Clk, D5 = SDO of first part, D4 = SDO of 2nd Part

Fclk = 35MHz Fsmpl = 100KSmpl/S,

Schematic is based on datasheet application (ADS8319 P 18)

Those issues, when append, are present on all frames all time (not a glitch or aleas).

by exchanging part issue is (are) solved.

Do you have some advice or track to understand that and correct it.

Thank you in advance

Alain