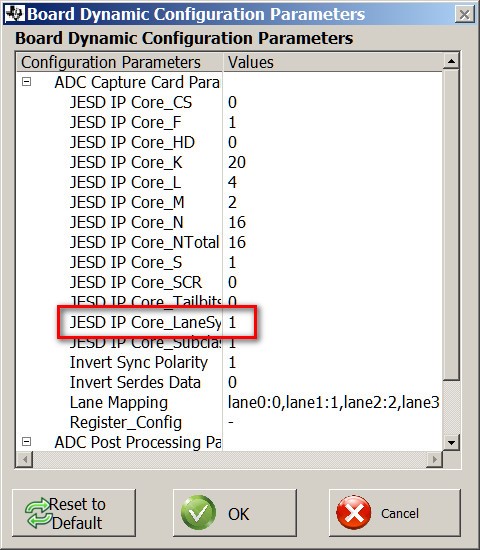

I'm using the TSW14J56EVM with a ADS32JB69EVM. When I select the ADS42JB69_LMF_421 and then look at the "Dynamic Configuration" dialog, there is an item "JESD IP Core_LaneSync" parameter that is set to 1. What is that parameter for? All the others make sense.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.