Hallo!

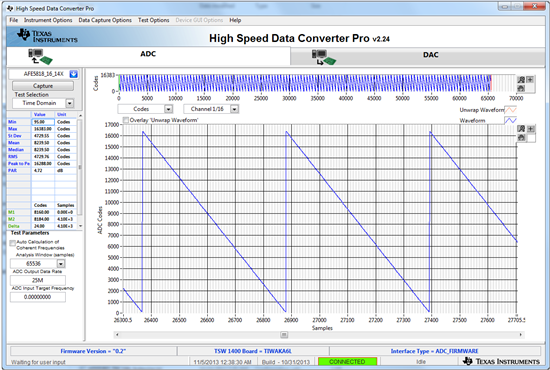

I am just sitting at ADS5263 EVM board tied up to Sparta-6 FPGA and try to connect these two. While observing the oscilloscope with fs = 2 MHz (low to get a good picture of all edges on the signals), I would to ask about the observed bahaviour:

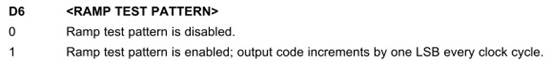

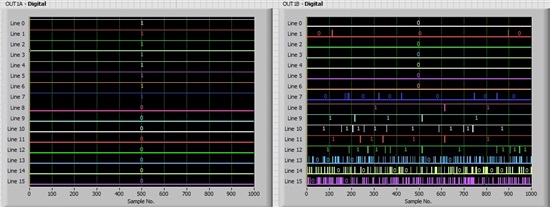

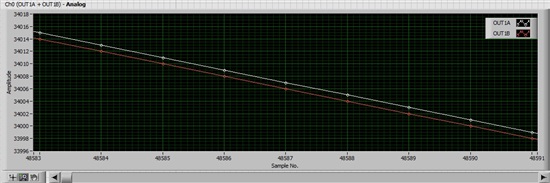

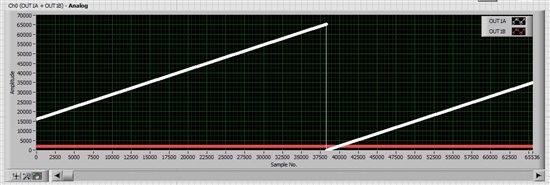

I see that the SYNC-PATTERN on OUT1A is always like 0xF0F0. My question, why does the pattern keep changing. I believe that in the WORD-WISE mode I should get a full sample within one period of of ADCLK clock. The settings are like this (ADS5263 EVM GUI app):

1a)ENABLE WORD-WISE CONTROL is ON

1b)2-wire 0.5x is switched into "0.5x Frame clock"

1c) Mapping of the channels is OFF

1d) LSB-First mode is selected

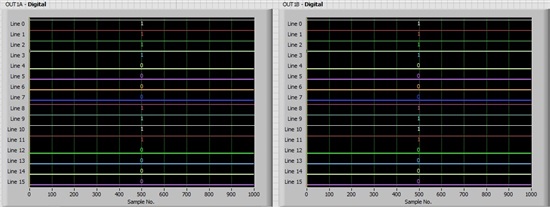

However, when I switch into "1x FrameClock" mode (I assume that I go into 1-wire mode doing this) I see that the pattern is like 0xFF00 -- as it should be.

What do I do wrong? Does the sync pattern deas depend on the 1-, 2-wire selection?

Regards

Pawel