Hi All,

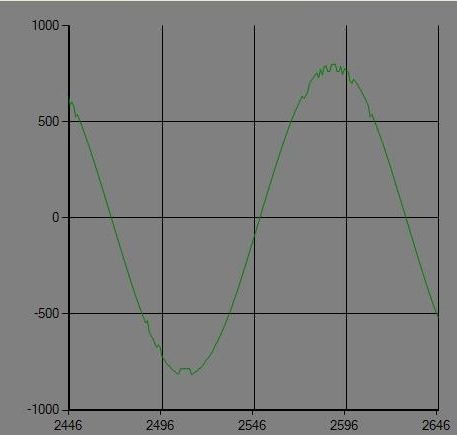

Our customer is evaluating ADC16DV160 on their board, but then they confirmed distortion on digital output as inserted waveform that is converted to analog waveform from digital output of ADC16DV160 by FPGA. They confirmed that the analog signal at input of ADC has no distortion so they think that this distortion may be occurred in ADC. Can you confirm following setting and give your comments?

[Setting]

- Input Range : 2.0Vpp (It can be also confirmed at 2.4Vpp)

- Input signal : 1.6Vpp, fixed 1MHz

- Sampling CLK : 1.4Vpp from Function Generator

[Behavior]

- The distortion is getting better at higher sampling frequency

- SFDR is also getting worse at higher sampling frequency

- -90dB @ 40Msps

- -83dB @ 80Msps

- -62dB @ 120Msps

- -45dB @ 160Msps

Please let me know if you need more information

Best Regards,

Sonoki / Japan Disty