Hi

We are using DAC7760 in our Analog Card design

Analog Card is placed on power supply module ( this will provide 5V to DAC ) and separate 24V given to Analog card ( through this +/- 15V is generated fro DAC )

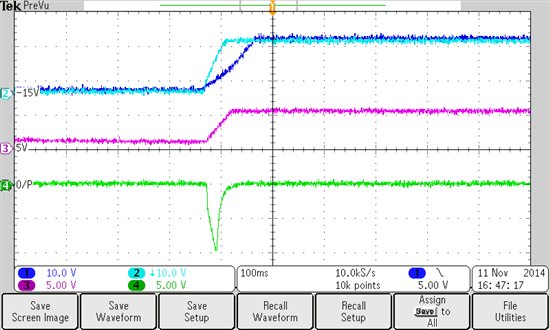

Now, when both Supplies are ON simultaneously, Glitch of -10V of 40ms is observed at DAC Output

What could be the reason?

Thank you,

Saurabh