Other Parts Discussed in Thread: ADS7229

Hi,

I have a question about behaviour of the ADC device ADS7229.

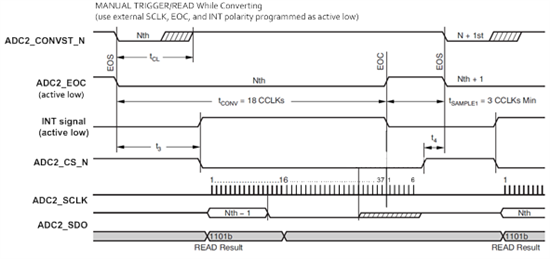

I want to control the device in manual trigger, read while converting, EOC/Int active low mode with EXTERNAL CLOCK.

For our case, the Internal clock should not be used.

The operation sequence that we want to implement is like the one explained in page 12 (figure 2) except for the use of internal clock.

If we want to do that with external SCLK, we need to provide the SCLK during the conversion time but what about the sampling time?

Should the external SCLK be generated during tSAMPLE?

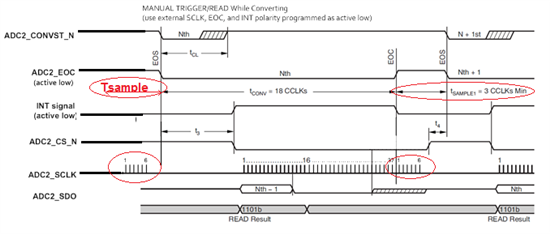

The data sheet does not give an example with external clock use so I proposed this sequence:

I added 6 SCLKs after conversion time for sampling however I think they should be added before the Nth pulse of CONVST_N. ( because for me the correct sequence is sampling then convst_n pulse ( for conversion) then after the next convst_n data can be read)

What do you think?

Any suggestion?

Thank you.