Hi,

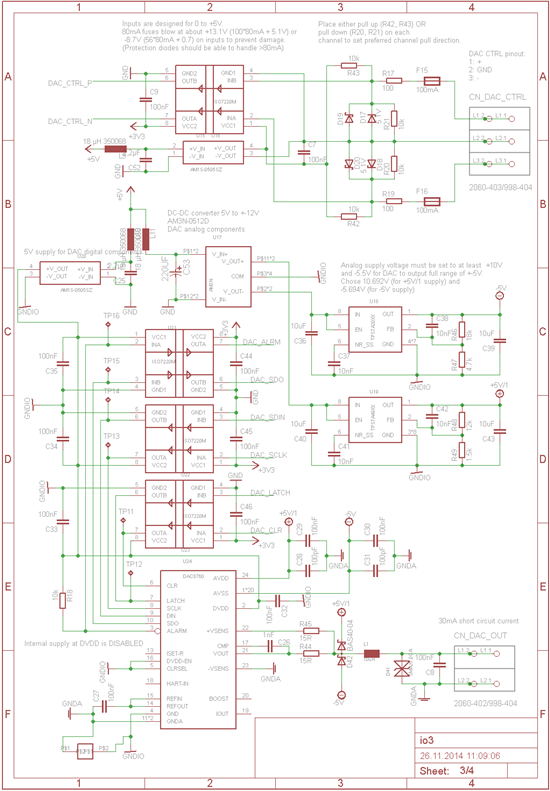

I'm trying to switch the voltage output of the DAC8760 to 0V and back to the previously set voltage by pulsing the CLR and LATCH pins as described in the data sheet on pages 11 (timing) and 36 (DAC CLEAR). The idea is to have a precision voltage source with asynchrounously switchable output.

Setting up the DAC output and clearing the output voltage with the CLR pin works fine, but I cannot restore the pre-clear value by "pulsing the LATCH signal". The output stays at 0V. I keep the SCLK pin low - so nothing gets clocked in. As it is I can only restore previous output via MCU by writing to the DAC register again. But this is way too slow to be of any use.

I use a FPGA to translate a digital input signal (hi = output 0V, lo = output voltage) to signals on CLR and LATCH.

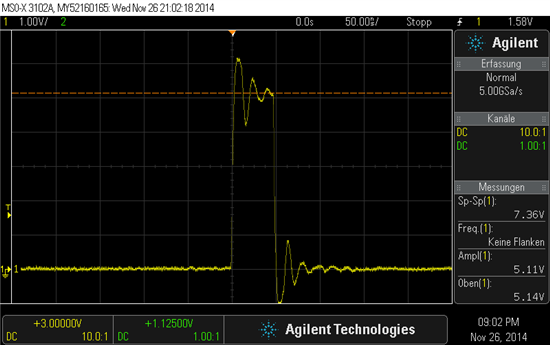

To switch the output to 0V I issue a 50ns pulse (hi) on CLR

To restore previous output I pulse LATCH for 83ns (hi).

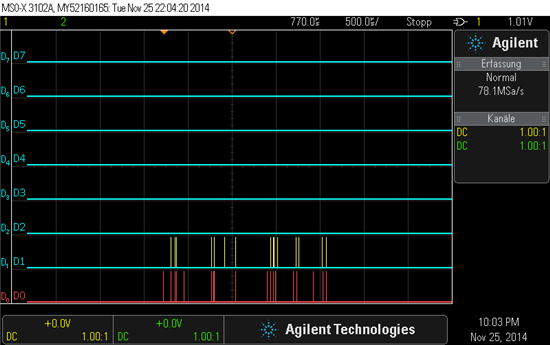

I connected the digital switch input to a pull up and to GND with a wire. If I put the wire in (output should switch on) I get this on LATCH and CLR pins (the port bounces):

D0 = LATCH; D1 = CLR; D2 = SCLK

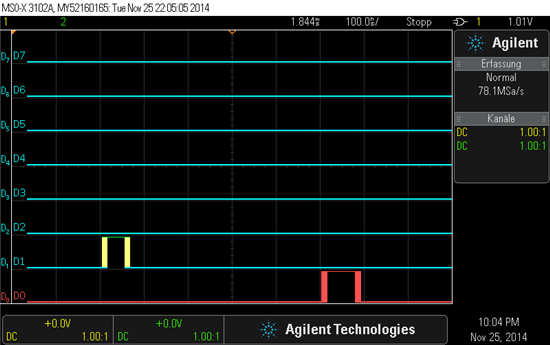

Zoom on last pair of pulses:

The FSM in the FPGA makes sure (and I checked this) that there is always a CLR pulse between 2 LATCH pulses or a LATCH pulse between 2 CLR pulses. As you can see the last pulse is on LATCH.

As I understood the datasheet this should restore output. Sooo... What did I miss? Why doesn't it work? Any hints and ideas are much appreciated.