I am reading 16 pressure sensors (flexiforce) with this chip. I use all 16 of the single-ended channels for this.

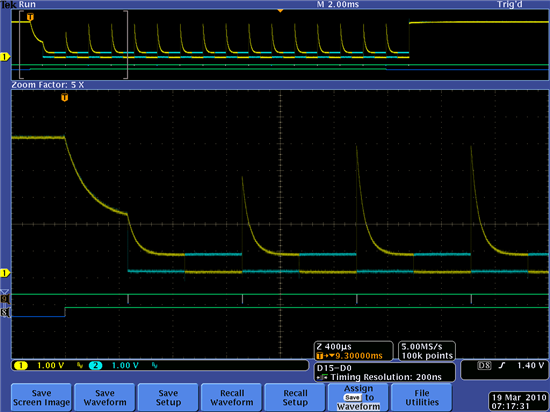

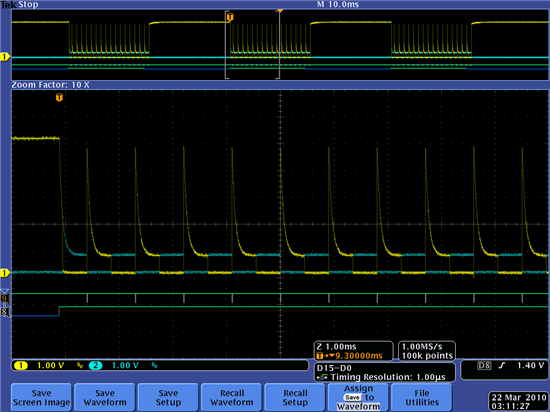

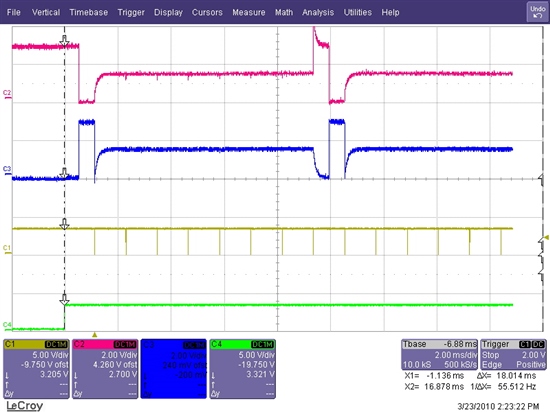

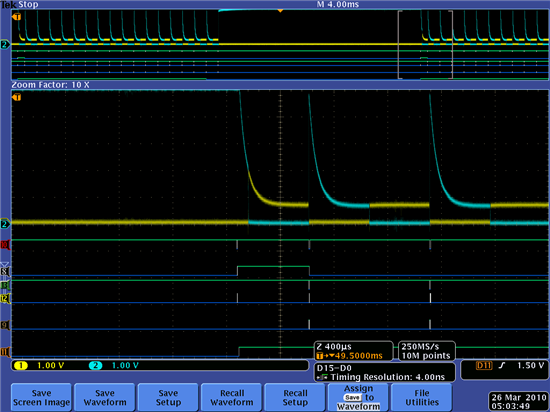

It appears that the first of the auto-scanned conversions does not get "chopped" correctly.

I have "fixed" the problem by inserting an initial dummy conversion of the DIFF0 channel, and discarding the result. Works, but hardly ideal. Am I doing something wrong?

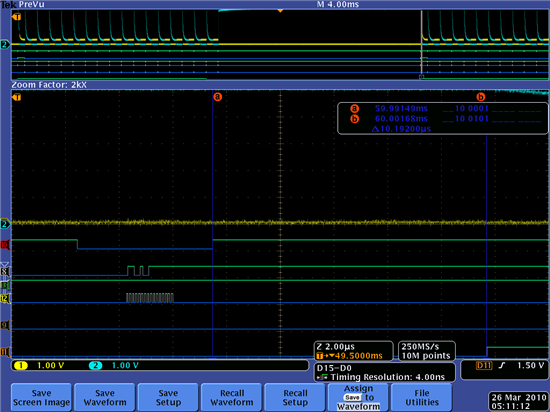

Attached is a scope picture showing what's happening. The bottom-most line, marked "8", is START. Above it, marked "9", is the DATA_READY signal. Yellow and blue are the positive and negative signals to be converted. This image is after the "fix", so the channel not being chopped is DIFF0. The subsequent channels are AIN0 - AIN15.

If more details will help, just ask.

Confused,

Brian