DEAR. ALL

Could help me

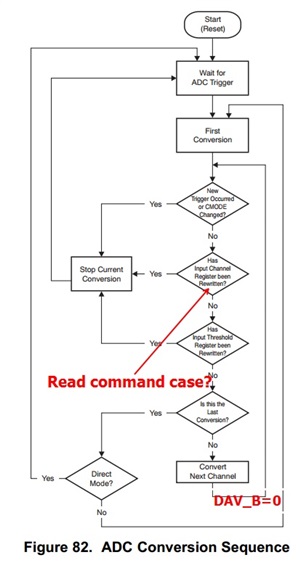

At the point of DAV_B=0 what recognized red column, does it take 1 usec for LOW of DAV_B pin?

How does ADC work out at the point of Read command case? or at the point of command registration which can read ADCn_data_register just ahead of DAV_B = 0?