Hello,

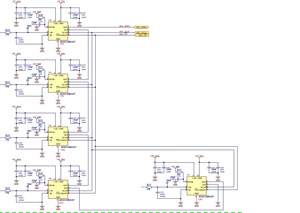

My project is proposing using 5 ADS8319 devices in "Daisy Chain Mode Without Busy Indicator".

We've never used these devices before and I would like to know if it is a reasonable solution to daisy chain 5 together, and if there are any constraints (hardware or software) that I am likely to encounter.

Regards,

Alan